FUJITSU F2MC-8L F202RA User Manual

Page 397

381

■

Explanation on the Codes Representing Instructions

Table B-1 describes the codes used to explain the instruction codes in Appendix B.

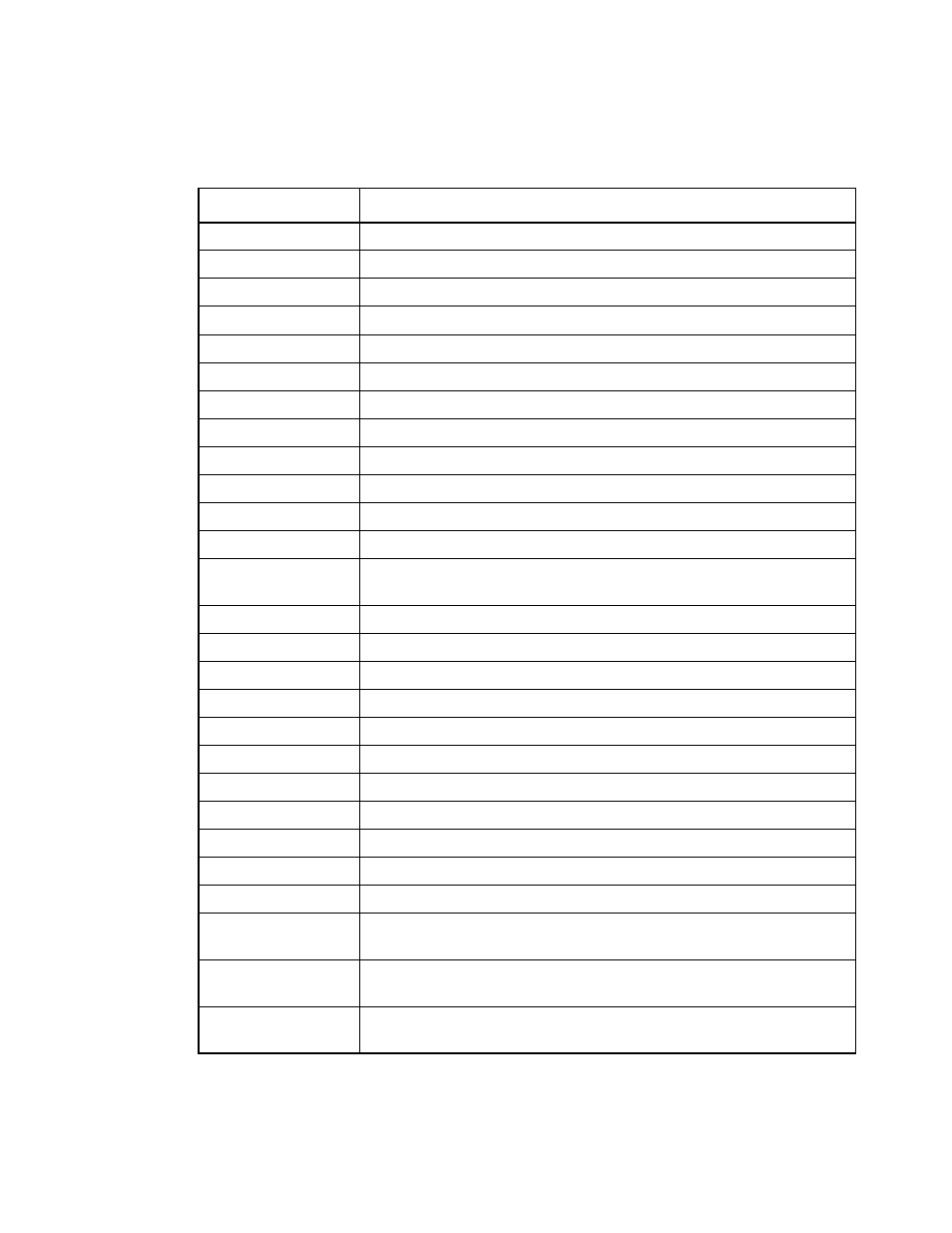

Table B-1 Explanation on Codes on Instructions’ List

Code

Meaning

dir

Direct address (8 bits)

off

Offset (8 bits)

ext

Extended address (16 bits)

#vct

Vector table number (3 bits)

#d8

Immediate data (8 bits)

#d16

Immediate data (16 bits)

dir:b

Bit direct address (8:3 bits)

rel

Branch relative address (8 bits)

@

Register indirect (Example: @A, @IX, and @EP)

A

Accumulator (8 bits or 16 bits, determined on basis of instruction to be used)

AH

Higher 8 bits of the accumulator (8 bits)

AL

Lower 8 bits of the accumulator (8 bits)

T

Temporary accumulator

(8 bits or 16 bits, determined on basis of instruction to be used)

TH

Higher 8 bits of the temporary accumulator (8 bits)

TL

Lower 8 bits of the temporary accumulator (8 bits)

IX

Index register (16 bits)

EP

Extra pointer (16 bits)

PC

Program counter (16 bits)

SP

Stack pointer (16 bits)

PS

Program status (16 bits)

dr

Either accumulator or index register (16 bits)

CCR

Condition code register (8 bits)

RP

Register bank pointer (5 bits)

Ri

General-purpose register (8 bits, i = 0 to 7)

X

Indicates that X itself is the immediate data.

(8 bits or 16 bits, determined on basis of instruction to be used)

(X)

Indicates that the contents of X is the accessing subject.

(8 bits or 16 bits, determined on basis of instruction to be used)

((X))

Indicates that the address specified in X is the accessing subject.

(8 bits or 16 bits, determined on basis of instruction to be used)