4 standby control register (stbc), Standby control register (stbc) – FUJITSU F2MC-8L F202RA User Manual

Page 82

66

CHAPTER 3 CPU

3.7.4

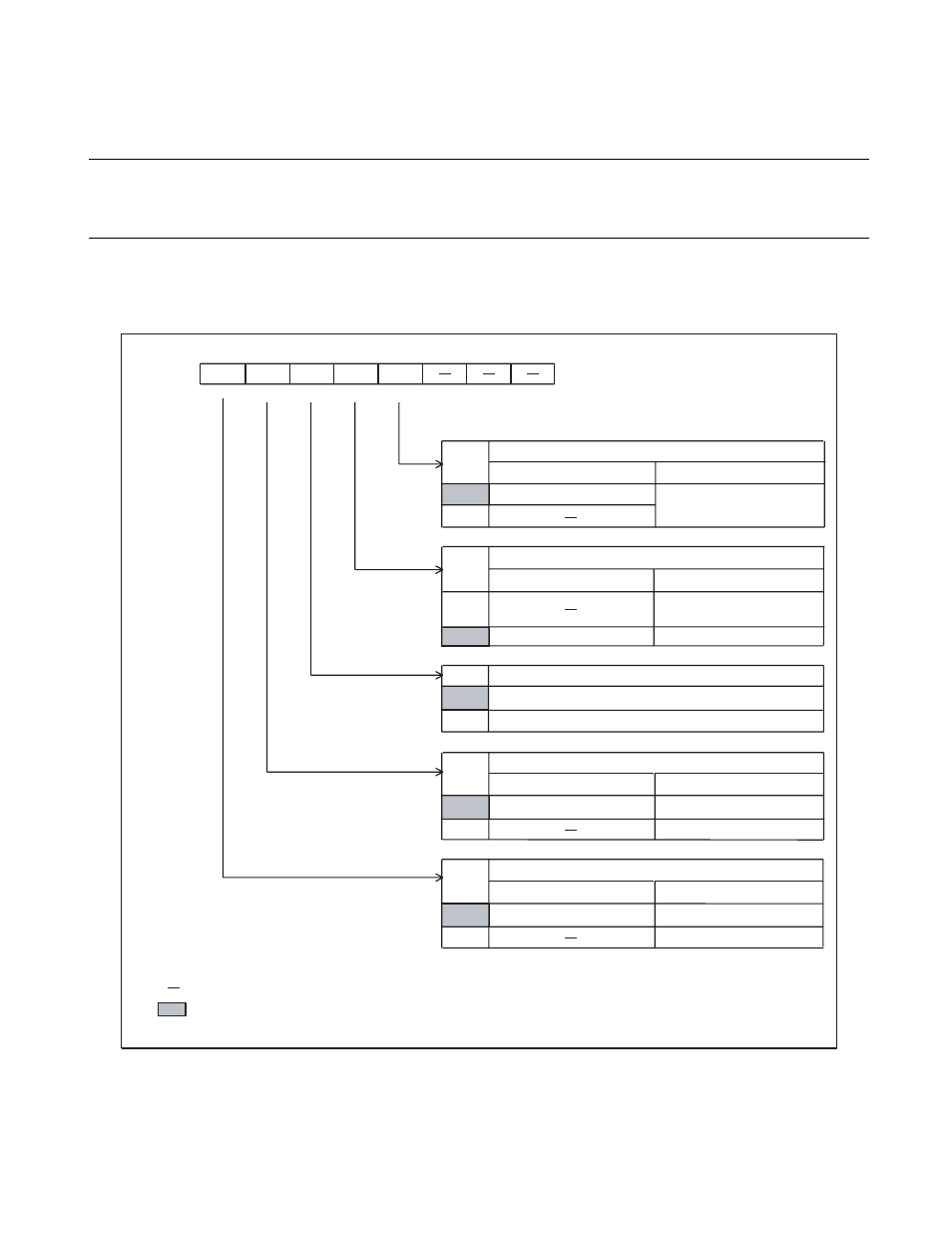

Standby Control Register (STBC)

The standby control register (STBC) controls transition to sleep /stop modes, pin state

settings in stop mode, and software reset.

■

Standby Control Register (STBC)

Figure 3.7-1 Standby Control Register (STBC)

RESV

0

1

RST

0

1

SPL

0

1

SLP

0

1

STP

0

1

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

0008

H

STP

SLP

SPL

RST RESV

00010---

B

R/W

R/W

R/W

R/W

R

R/W

: Read only

: Unused

: Initial value

R

: Readable/Writable

Address

Initial value

Reserved bit

When read

When read

When read

When read

When written

When written

When written

When written

Always "0"

Does not affect operations

Software reset bit

4-instruction reset signal

generated.

Always "1"

Does not affect operations

Pin state setting bit

Pin states applied are maintained in stop mode.

Pin states are set to Hi-Z in stop mode.

Sleep bit

Always "0"

Does not affect operations

Transition to sleep mode

Stop bit

Always "0"

Does not affect operations

Transition to stop mode