3 system clock control register (sycc), System clock control register (sycc) – FUJITSU F2MC-8L F202RA User Manual

Page 72

56

CHAPTER 3 CPU

3.6.3

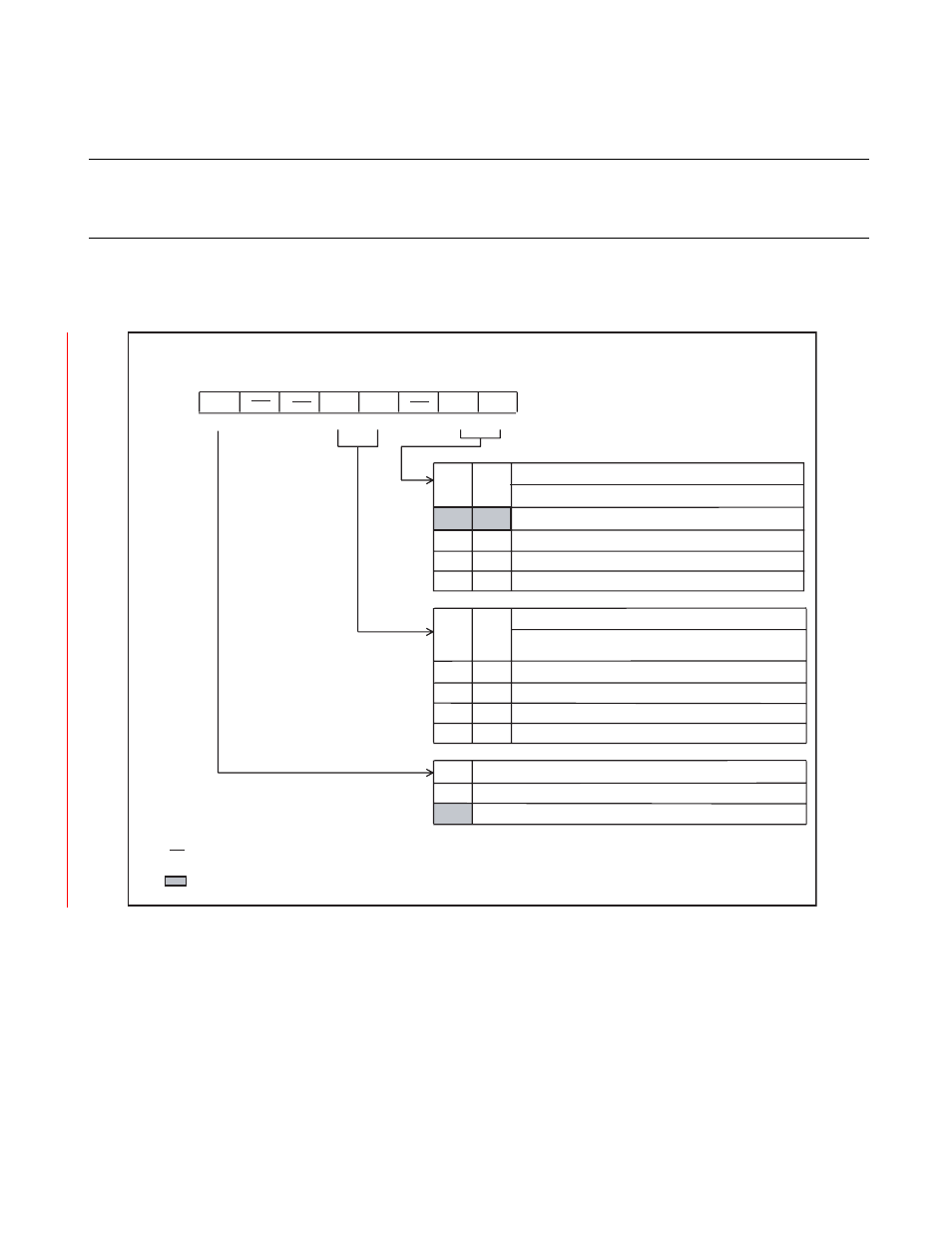

System Clock Control Register (SYCC)

The system clock control register (SYCC) manages clock settings such as selection of

the clock speed and oscillation stabilization wait time.

■

Configuration of the System Clock Control Register (SYCC)

Figure 3.6-5 Configuration of System Clock Control Register (SYCC)

C

S

1 C

S

0

0

0

64/F

CH

(5.12

µ

s

)

0

1

16/F

CH

(1.2

8

µ

s

)

1

0

8

/F

CH

(0.64

µ

s

)

1

1

4/F

CH

(0.

3

2

µ

s

)

WT1 WT0

0

0

0

1

1

0

1

1

b

it7

b

it6

b

it5

b

it4

b

it

3

b

it2

b

it1

b

it0

0007

H

WT1

S

CM

WT0

C

S

1

C

S

0 1--MM-00

B

R/W

R

R/W

R/W

R/W

R

: Re

a

d only

R/W : Re

a

d

ab

le/Writ

ab

le

: Un

us

ed

M : M

as

k option

: Initi

a

l v

a

l

u

e

Addre

ss

Initi

a

l v

a

l

u

e

Clock

s

peed

s

election

b

it

s

In

s

tr

u

ction cycle (when F

CH

i

s

12.5 MHz)

O

s

cill

a

tion

s

t

ab

iliz

a

tion w

a

it time

s

election

b

it

s

O

s

cill

a

tion

s

t

ab

iliz

a

tion w

a

it time

a

ccording to

o

u

tp

u

t of the time-

bas

e timer (when F

CH

i

s

12.5 MHz)

S

etting prohi

b

ited

Approx. 2

14

/F

CH

(

a

pprox. 1.

3

1 m

s

)

Approx. 2

17

/F

CH

(

a

pprox. 10.5 m

s

)

Approx. 2

1

8

/F

CH

(

a

pprox. 21.0 m

s

)

S

CM

0

1

S

y

s

tem clock monitor

b

it

Clock

s

topping or w

a

iting for

s

t

ab

iliz

a

tion of o

s

cill

a

tion

Active mode