2 register bank pointer (rp), Register bank pointer (rp), Section "3.2.2 register bank pointer (rp) – FUJITSU F2MC-8L F202RA User Manual

Page 47: Configuration of the register bank pointer (rp)

31

CHAPTER 3 CPU

3.2.2

Register Bank Pointer (RP)

The register bank pointer (RP) is the upper 8 bits of the program status register (PS).

The register bank pointer indicates the general-purpose register bank address being

used, and the address is converted to the actual address in general-purpose register

addressing.

■

Configuration of the Register Bank Pointer (RP)

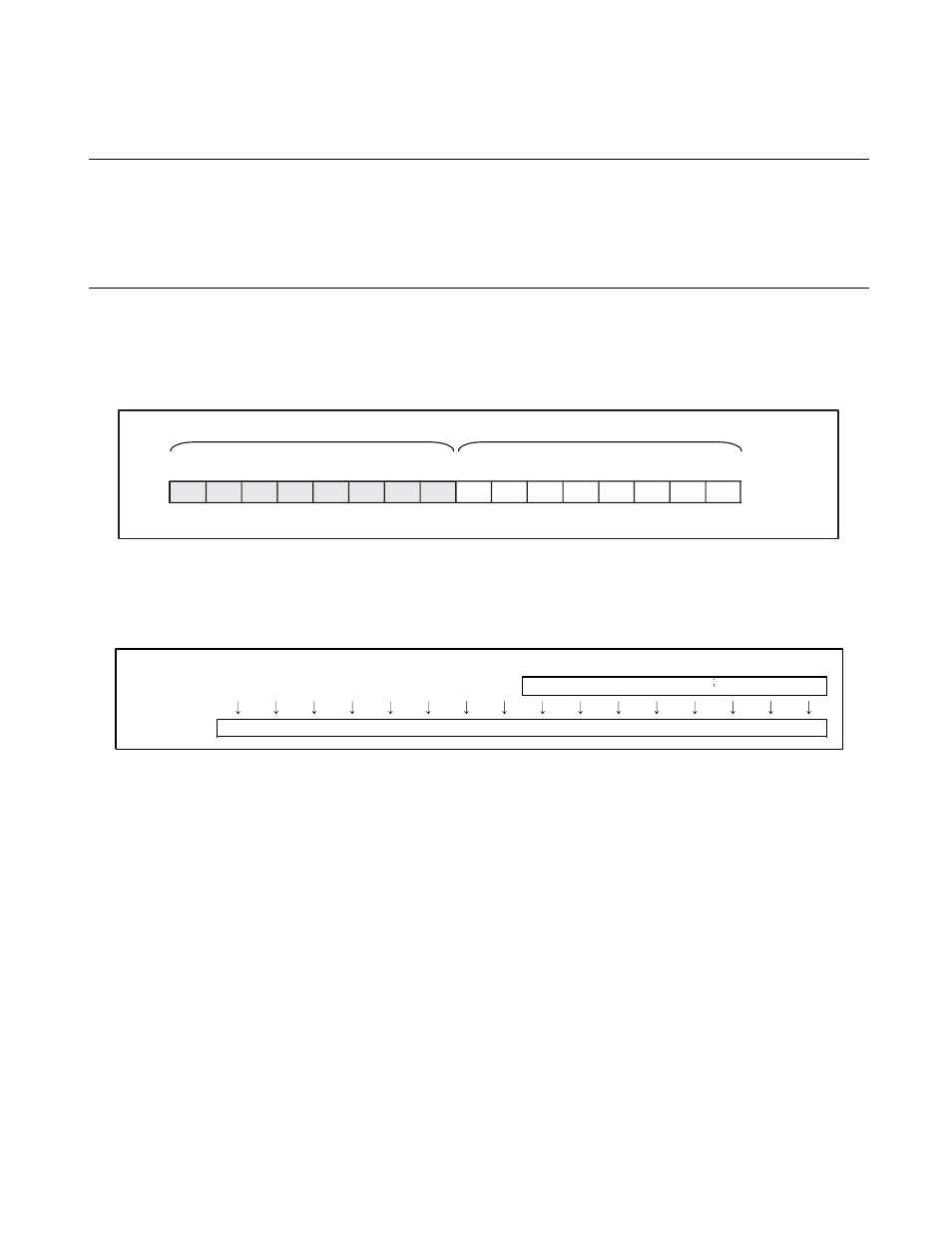

Figure 3.2-4 shows the configuration of the register bank pointer.

Figure 3.2-4 Configuration of Register Bank Pointer

The register bank pointer indicates the address of the register bank being used. Figure 3.2-5 shows the rule

of conversion from the register bank pointer bits to the actual address.

Figure 3.2-5 Rule of Conversion from the RP Bits to the Actual Address

The register bank pointer specifies a memory block (register bank) used as a general-purpose register in the

RAM area. There are 32 register banks. Setting a value (from 0 to 31) in the upper five bits of the register

bank pointer specifies a register bank. One register bank contains eight 8-bit general-purpose registers that

are selected with the lower 3 bits of an operation code.

The register bank pointer allows a range of 0100

H

to 01FF

H

(maximum) to be used as the general-purpose

register area. However, some models restrict the usable range when only internal RAM is used. The initial

value of the register bank pointer specified after the reset operation is undefined.

Note:

Be sure to set up the register bank pointer (RP) before using general-purpose registers.

The register bank pointer is part of the program status register (PS), and thus is not allowed to access

only the register bank pointer.

RP

CCR

bit15

bit14 bit13 bit12 bit11 bit10

bit9

bit8

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

PS

R4

R3

R2

R1

R0

-

-

-

H

I

IL1

IL0

N

Z

V

C

XXXXXXXX

B

RP initial value

X: Undefined

R4

R3

R2

R1

R0

b2

b1

b0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

"0"

RP upper bits

Lower bits of operation code

Address

generated

"0"

"0"

"0"

"0"

"0"

"0"

"1"