6 clock divider selection register (upc), Clock divider selection register (upc) – FUJITSU F2MC-8L F202RA User Manual

Page 315

299

CHAPTER 13 UART

13.4.6

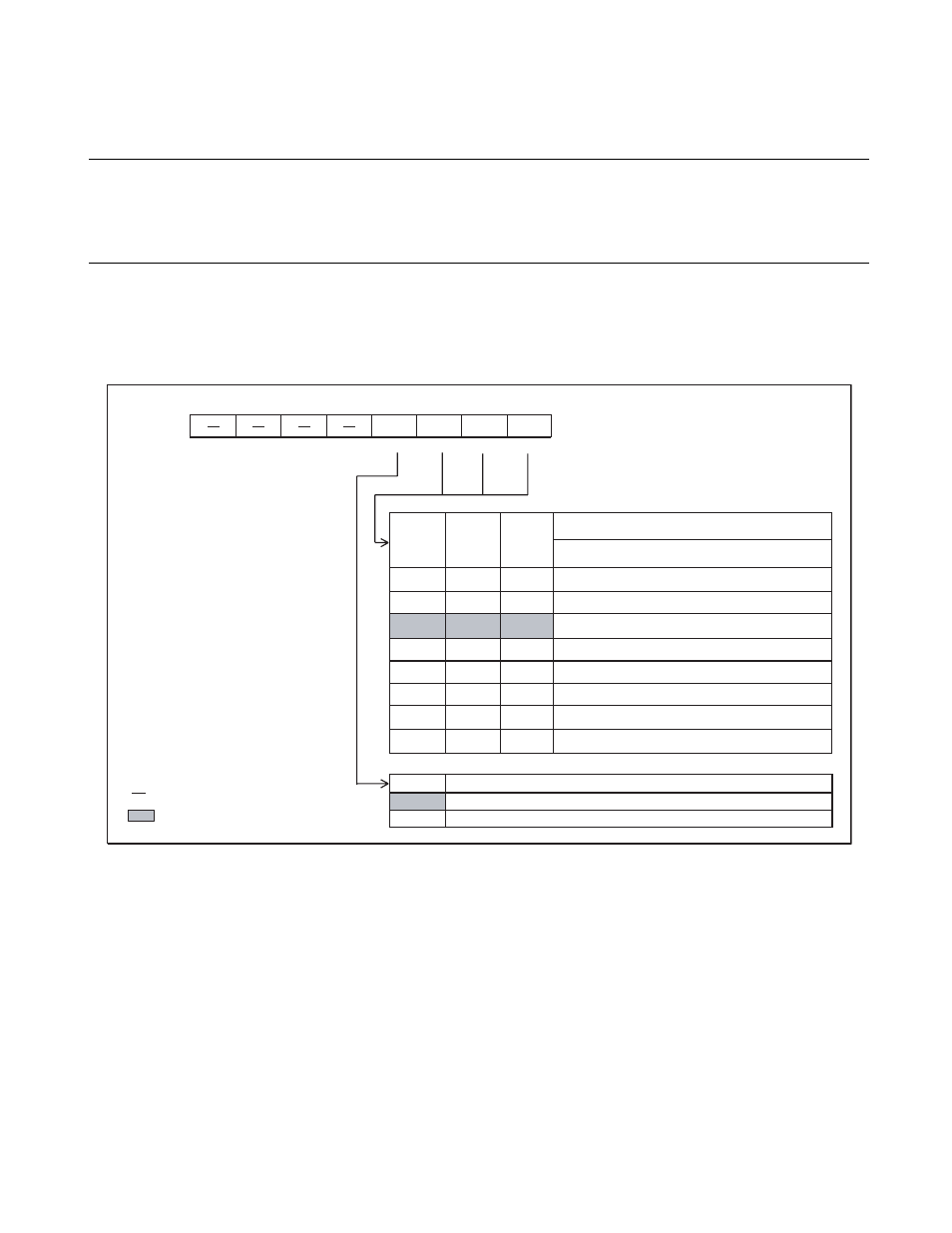

Clock Divider Selection Register (UPC)

The clock divider selection register is used to generate the UART reference clock by

dividing the oscillation frequency. It also enables/disables operation of the prescaler for

creating the reference clock.

■

Clock Divider Selection Register (UPC)

Figure 13.4-8 Clock Divider Selection Register (UPC)

PR2

PR1

PR0

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

PREN

0

1

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

002C

H

PREN

PR2

PR1

PR0

----0010

B

R/W

R/W

R/W

R/W

R/W

Address

Initial value

Clock divider selection bits

Divider

Divides the clock by 1.

Divides the clock by 2.

Divides the clock by 2.5.

Divides the clock by 3.

Divides the clock by 4.

Divides the clock by 5.

Do not specify this setting.

Do not specify this setting.

UART prescaler operation enable bit

Disables the prescaler operation.

Enables the prescaler operation.

: Readable/Writable

: Unused

: Initial value

1