FUJITSU F2MC-8L F202RA User Manual

Page 233

217

CHAPTER 9 12-BIT PPG TIMER

Note:

Because buzzer outputs to the P37/BZ/PPG pin precede 12-bit PPG outputs to this pin, if the pin is used

as the PPG pin, turn the buzzer outputs off and set the RCEN bit such that PPG outputs are enabled.

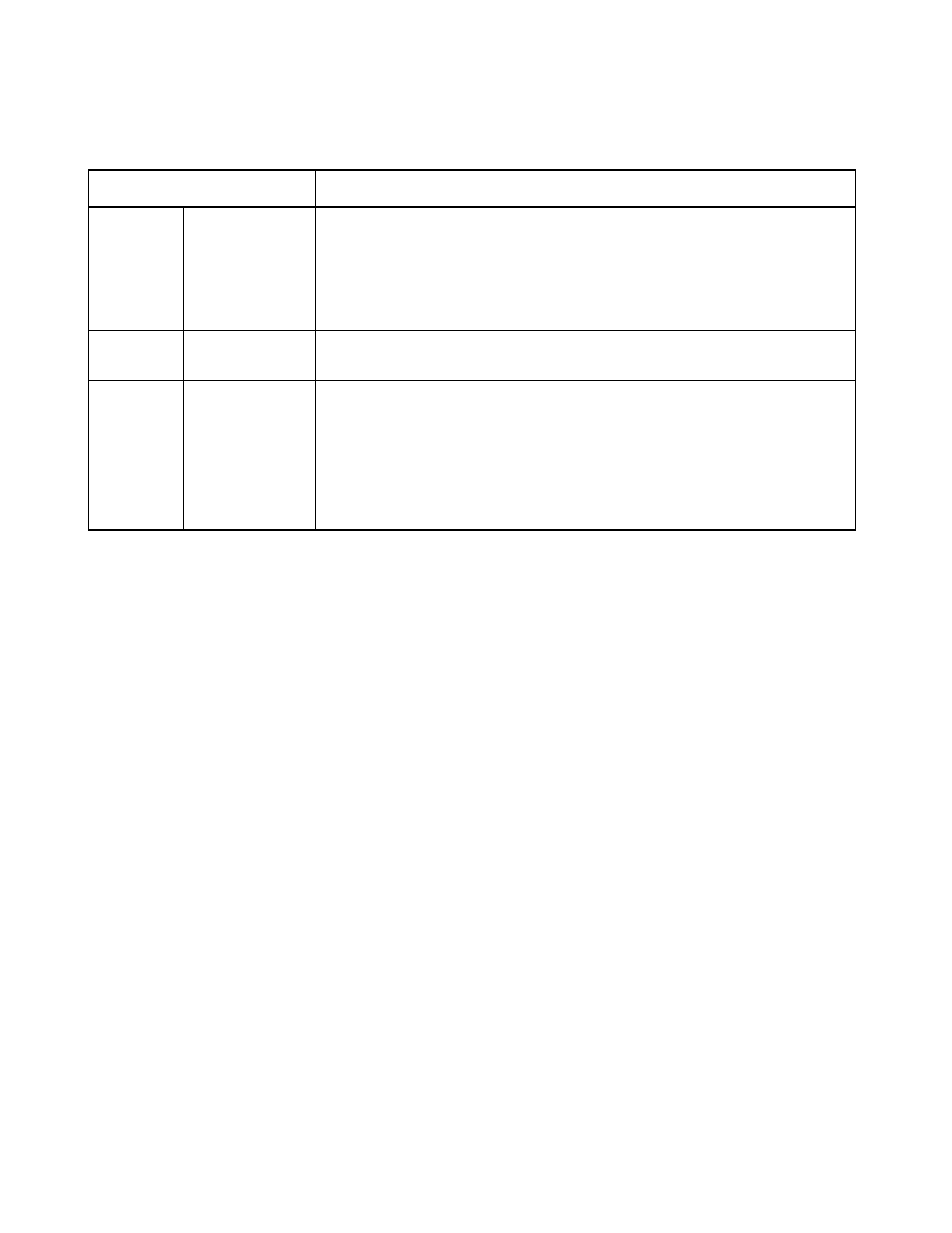

Table 9.4-3 Explanation of Functions of Each Bit in 12-bit PPG Control Register 3 (RCR23)

Bit name

Function

bit7

RCEN:

Output enable bit

When this bit is "0", the P37/BZ/PPG pin functions as a general-purpose port (P37);

when the bit is "1", the pin functions as a 12-bit PPG output pin (PPG).

When "0" is written for this bit, the counter is cleared and its operation stops; when

"1" is written, the count operation starts.

Even if PPG outputs are enabled by this bit setting, buzzer outputs, if enabled, have

priority.

bit6

Unused bit

•

Bit value is undefined when being read.

•

Written value does not affect other operations.

bit5

to

bit0

SCL5 to SCL0:

Cycle period

setting bits

These bits are used to set the number of counts corresponding to the cycle period of

12-bit PPG waveform outputs (the compare value for the cycle period), and the

contents of these bits and the SCL6 to SCL11 bits of RCR24 are compared with a

count by the counter.

Note:

Set a value that falls within the range of "000000000010

B

" to "111111111111

B

"

(002

H

to FFF

H

).