4 interrupt processing time, Interrupt processing time – FUJITSU F2MC-8L F202RA User Manual

Page 56

40

CHAPTER 3 CPU

3.4.4

Interrupt Processing Time

From when an interrupt request is generated to when control is transferred to the

interrupt processing routine, both the time to quit the instruction being executed and

the time to manage the interrupt (required to prepare interrupt processing) are required.

The total time must be within 30 instruction cycles.

■

Interrupt Processing Time

From when an interrupt request is generated and accepted to when the interrupt processing routine starts,

sufficient time is required to wait for an interrupt request sample and to manage the interrupt.

●

Interrupt request sample wait time

Generation of an interrupt request is checked by sampling an interrupt request at the last cycle of each

instruction. Therefore, the CPU cannot identify an interrupt request while it is executing an instruction. The

wait time becomes maximum when an interrupt request is generated immediately after the CPU executes

the DIVU instruction (21 instruction cycles) with the longest instruction cycle.

●

Interrupt handling time

After accepting an interrupt, the CPU needs 9 instruction cycles for interrupt processing preparation to:

•

Save the values in the program counter (PC) and program status (PS)

•

Set the address at the beginning of the interrupt processing routine (interrupt vector) into the PC

•

Update the interrupt level bits (PS: CCR: IL1 and IL0) in the program status (PS).

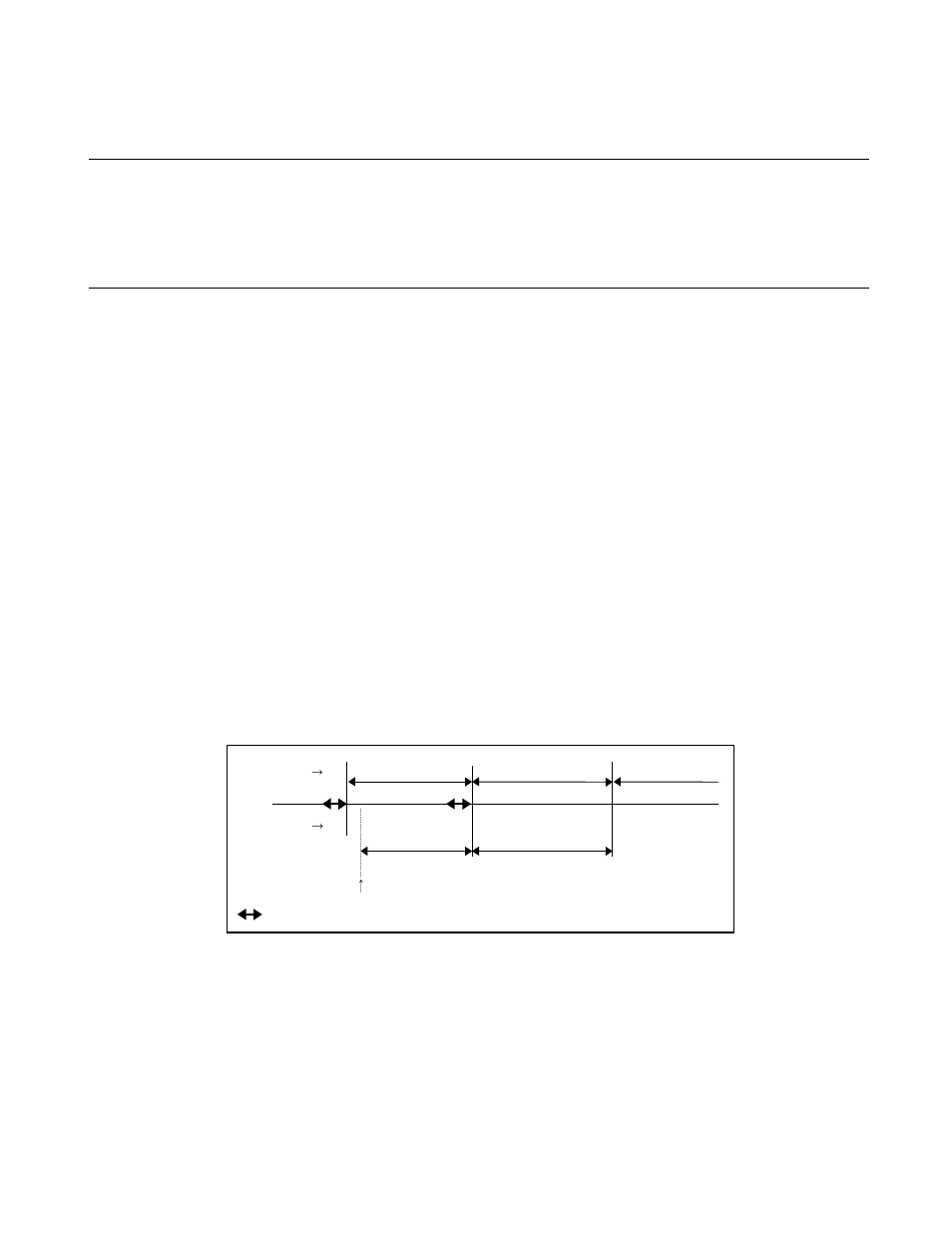

Figure 3.4-4 shows the interrupt processing time.

Figure 3.4-4 Interrupt Processing Time

When an interrupt request is generated immediately after the DIVU instruction having the longest

instruction cycle (21 instruction cycles), 30 instruction cycles (21 instructions + 9 instructions) are required

for the interrupt processing time. However, if the DIVU instruction and MULU instruction are not used in

the program, a maximum of 15 (6 instructions + 9 instructions) instructions are required for the instruction

processing time.

An instruction cycle is changed by clock speed switching (gears). For details, see Section "3.6 Clock ".

CPU performs

Interrupt wait

time

Execution of

general instruction

Interrupt request

sample wait time

Interrupt handling

Interrupt handling time

(9 instruction cycles)

Interrupt processing

routine

Interrupt request is generated

: Last instruction in which an interrupt is sampled