5 interrupt of 8-bit serial i/o, Interrupt of 8-bit serial i/o – FUJITSU F2MC-8L F202RA User Manual

Page 340

324

CHAPTER 14 8-BIT SERIAL I/O

14.5

Interrupt of 8-Bit Serial I/O

An 8-bit serial I/O interrupt is caused by completion of 8-bit serial data I/O.

■

Interrupt at Serial I/O Operation

In the 8-bit serial I/O, serial output operation and serial input operation are performed at the same time.

When serial I/O transfer is started, the values in the serial data register (SDR) are input and output on a per

bit basis in synchronization with the set shift clock cycle. When the shift clock of the 8th bit rises, the

interrupt request flag bit (SMR: SIOF) is set to "1".

In this case, when the interrupt request output allowance bit is allowed (SMR: SIOE = 1), the interrupt

request (IRQC) for CPU interrupt occurs.

Write "0" to the SIOF bit with the interrupt processing routine and clear the interrupt request. When 8-bit

serial output is completed, the SIOF bit is set irrespective of the SIOE bit value.

If serial I/O transfer stop (SMR: SST = 0) and serial data transfer termination take place at the same time

during serial I/O operation, the interrupt request flag bit (SMR: SIOF = 1). If the SIOE bit is allowed (0

→

1), however, the interrupt request occurs immediately.

■

8-bit Serial I/O Interrupt Register and Vector Table

For interrupt operation, see Section "3.4.2 Steps in the Interrupt Operation ".

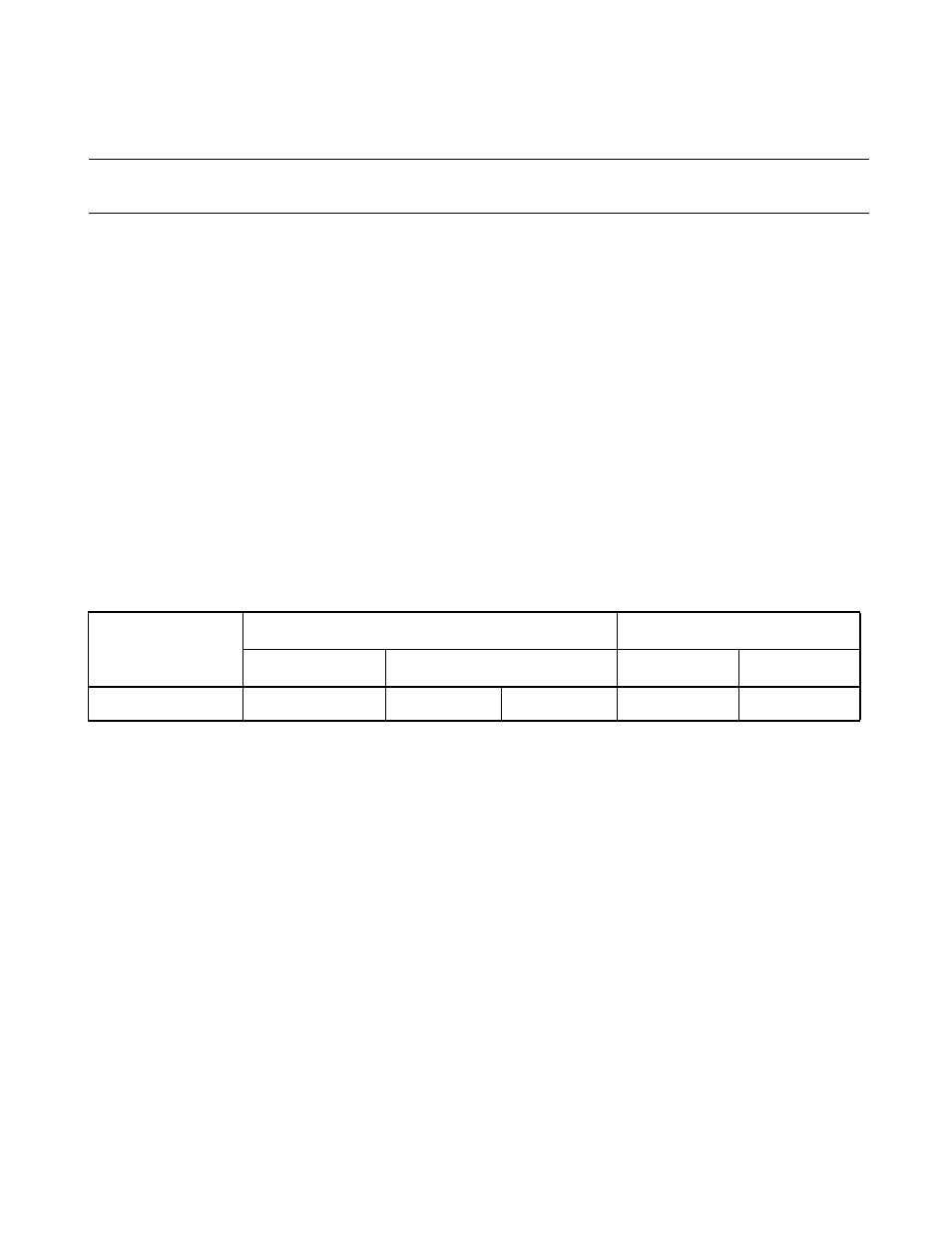

Table 14.5-1 8-bit Serial I/O Interrupt Register and Vector Table

Interrupt name

Interrupt level setting register

Vector table address

Register

Setting bit

Higher

Lower

IRQC

ILR4 (007E

H

)

LC1 (bit1)

LC0 (bit0)

FFE2

H

FFE3

H