Determining the synchronous transfer rate, Figure 2.7 – Avago Technologies LSI53C895A User Manual

Page 67

SCSI Functional Description

2-41

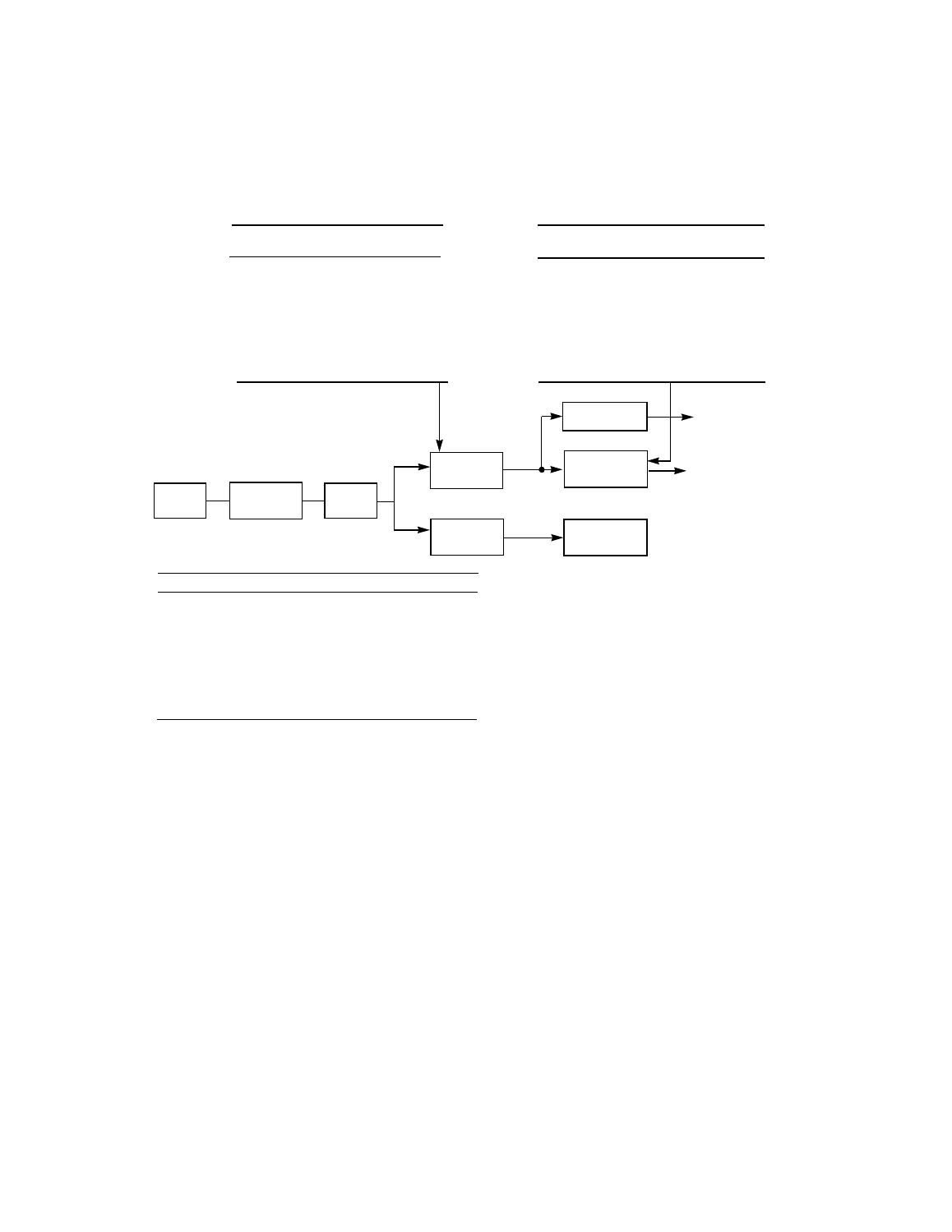

Figure 2.7

Determining the Synchronous Transfer Rate

2.2.15.2

Register, Bits [6:4] (SCF[2:0])

The SCF[2:0] bits select the factor by which the frequency of SCLK is

divided before being presented to the synchronous SCSI control logic.

The output from this divider controls the rate at which data can be

received; this rate must not exceed 160 MHz. The receive rate of

synchronous SCSI data is one-fourth of the SCF divider output. For

example, if SCLK is 160 MHz and the SCF value is set to divide by one,

then the maximum rate at which data can be received is 40 MHz

(160/(1*4) = 40).

SCLK

Clock

Quadrupler

QCLK

SCF

Divider

CCF

Divider

Synchronous

Divider

Asynchronous

SCSI Logic

Divide by 4

SCF2

SCF1

SCF0

SCF

Divisor

0

0

1

1

0

1

0

1.5

0

1

1

2

1

0

0

3

0

0

0

3

1

0

1

4

1

1

0

6

1

1

1

8

TP2

TP1

TP0

XFERP

Divisor

0

0

0

4

0

0

1

5

0

1

0

6

0

1

1

7

1

0

0

8

1

0

1

9

1

1

0

10

1

1

1

11

CCF2

CCF1

CCF0

Divisor

QCLK (MHz)

0

0

1

1

50.1–66.00

0

1

0

1.5

16.67–25.00

0

1

1

2

25.1–37.50

1

0

0

3

37.51–50.00

0

0

0

3

50.01–66.00

1

0

1

4

75.01–80.00

1

1

0

6

120

1

1

1

8

160

Example:

QCLK (Quadrupled SCSI Clock) = 160 MHz

SCF = 1 (/1), XFERP = 0 (/4), CCF = 7 (/8)

Synchronous send rate = (QCLK/SCF)/XFERP =

(160/1) /4 = 40 Mbytes/s

Synchronous receive rate = (QCLK/SCF) /4 =

(160/1) /4 = 40 Mbytes/s

This point

must not

exceed

160 MHz

Receive

Clock

Send Clock

(to SCSI Bus)