Scsi timer zero (stime0), Register: 0x48 – Avago Technologies LSI53C895A User Manual

Page 193

SCSI Registers

4-85

GPIO

GPIO Enable

[1:0]

These bits power-up set, causing the GPIO1 and GPIO0

pins to become inputs. Clearing these bits causes

GPIO[1:0] to become outputs.

Register: 0x48

SCSI Timer Zero (STIME0)

Read/Write

HTH[3:0]

Handshake-to-Handshake Timer Period

[7:4]

These bits select the handshake-to-handshake time-out

period, the maximum time between SCSI handshakes

(SREQ/ to SREQ/ in target mode, or SACK/ to SACK/ in

initiator mode). When this timing is exceeded, an interrupt

is generated and the HTH bit in the

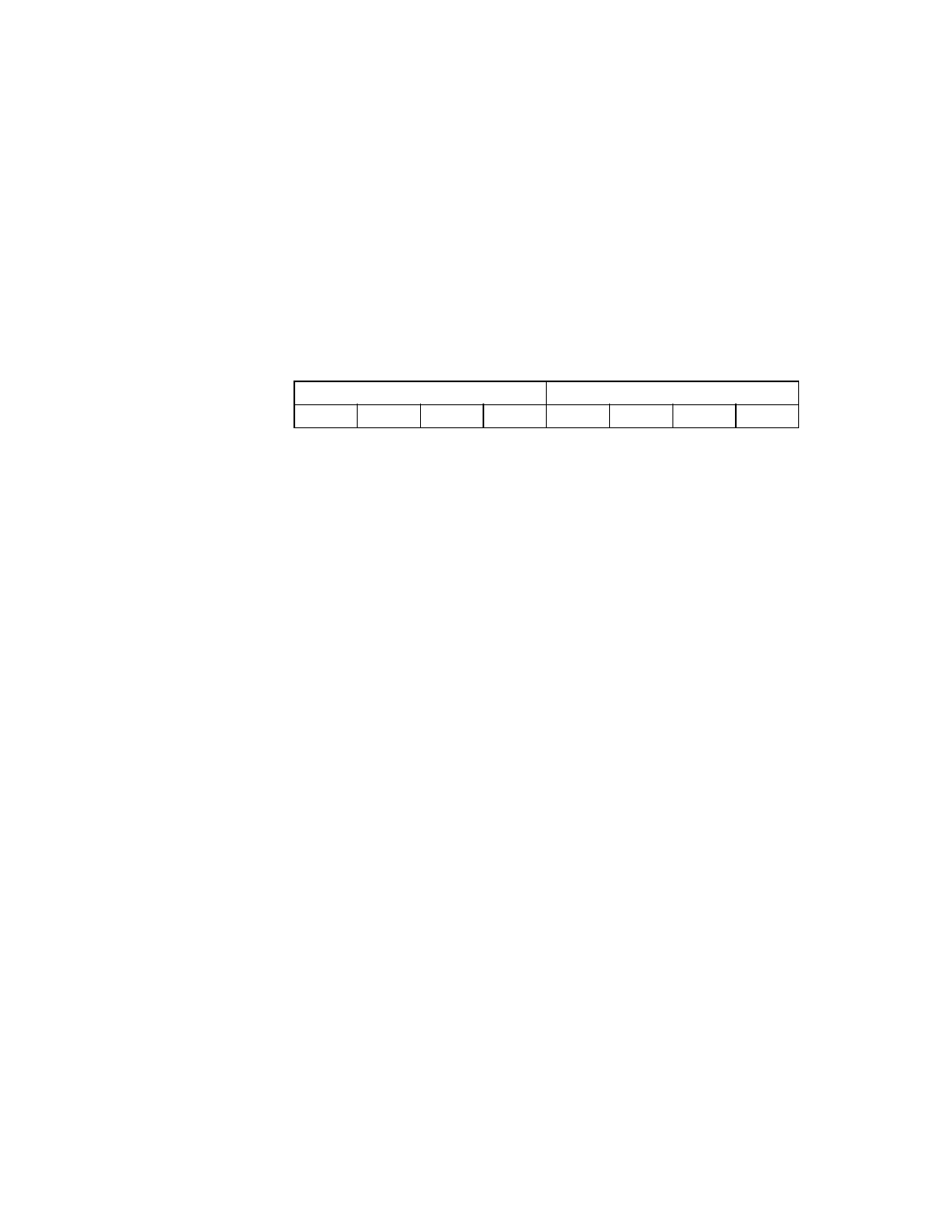

register is set. The following table contains

time-out periods for the Handshake-to-Handshake Timer,

the Selection/Reselection Timer (bits [3:0]), and the

General Purpose Timer (

(bits [3:0]). For a more detailed explanation of interrupts,

refer to

Chapter 2, “Functional Description.”

7

4

3

0

HTH[3:0]

SEL[3:0]

0

0

0

0

0

0

0

0

- MGA-725M4 (4 pages)

- MGA-71543 (4 pages)

- MGA-71543 (3 pages)

- MGA-82563 (6 pages)

- 3ware SAS 9750-8i (48 pages)

- 3ware 9690SA-8I (Channel) (138 pages)

- 3ware 9690SA-8I (Channel) (380 pages)

- 3ware SAS 9750-8i (29 pages)

- 3ware 9550SXU-8LP (Channel) (149 pages)

- 3ware 9550SXU-8LP (Channel) (40 pages)

- 3ware 9650SE-8LPML (Channel) (45 pages)

- 3ware 9690SA-8I (Channel) (27 pages)

- 3ware 9690SA-8I (Channel) (361 pages)

- 6160 SAS Switch (2 pages)

- MegaRAID SAS 9380-8e (43 pages)

- Cache Protection for RAID Controller Cards (139 pages)

- Cache Protection for RAID Controller Cards (13 pages)

- MegaRAID SAS 9271-8iCC (13 pages)

- MegaRAID SAS 9361-8i (13 pages)

- MegaRAID SAS 9266-8i (12 pages)

- MegaRAID SAS 9266-8i (20 pages)

- MegaRAID SAS 9271-8iCC (26 pages)

- MegaRAID SafeStore Software (502 pages)

- MegaRAID SAS 9285-8ecv (80 pages)

- MegaRAID SAS 9285-8ecv (92 pages)

- MegaRAID SAS 0260CV-4i (49 pages)

- MegaRAID SAS 9271-8i (8 pages)

- MegaRAID SAS 0260CV-4i (72 pages)

- MegaRAID SAS 0260CV-4i (64 pages)

- MegaRAID SAS 9361-8i (7 pages)

- MegaRAID SAS 9341-8i (8 pages)

- MegaRAID SAS 9380-4i4e (7 pages)

- MegaRAID SAS 9380-8e (7 pages)

- MegaRAID SAS 0260CV-4i (28 pages)

- MegaRAID SAS 9240-8i (4 pages)

- MegaRAID SAS 9280-24i4e (14 pages)

- MegaRAID SAS 9280-24i4e (16 pages)

- MegaRAID SAS 9260-16i (12 pages)

- MegaRAID SafeStore Software (8 pages)

- MegaRAID SAS 9280-8e (22 pages)

- MegaRAID SAS 9260-8i (4 pages)

- MegaRAID SAS 9261-8i (4 pages)

- MegaRAID SAS 9285-8e (12 pages)

- MegaRAID SAS 9280-16i4e (12 pages)

- MegaRAID SAS 9280-4i4e (4 pages)