Scsi test three (stest3), Scsi test, Three (stest3) – Avago Technologies LSI53C895A User Manual

Page 201: Scsi, Test three (stest3), Register: 0x4f

SCSI Registers

4-93

Note:

Never set this bit during fast SCSI (greater than 5 Mbyte

transfers per second) operations, because a valid assertion

could be treated as a glitch.

LOW

SCSI Low level Mode

0

Setting this bit places the LSI53C895A in the low level

mode. In this mode, no DMA operations occur, and no

SCRIPTS execute. Arbitration and selection may be

performed by setting the start sequence bit as described

in the

register. SCSI bus

transfers are performed by manually asserting and polling

SCSI signals. Clearing this bit allows instructions to be

executed in SCSI SCRIPTS mode.

Note:

It is not necessary to set this bit for access to the SCSI

bit-level registers

, and input registers.

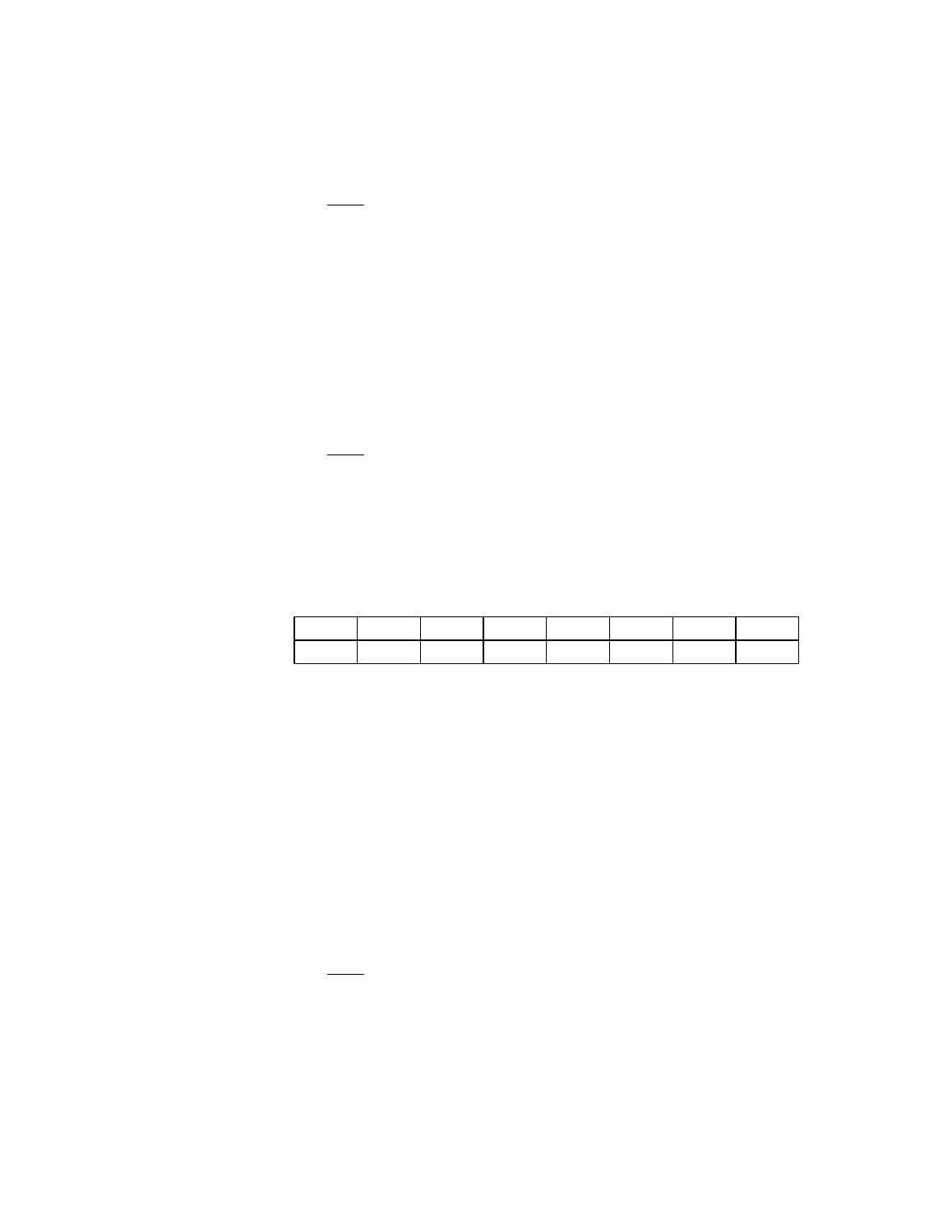

Register: 0x4F

SCSI Test Three (STEST3)

Read/Write

TE

TolerANT Enable

7

Setting this bit enables the active negation portion of

LSI Logic TolerANT technology. Active negation causes

the SCSI Request, Acknowledge, Data, and Parity

signals to be actively deasserted, instead of relying on

external pull-ups, when the LSI53C895A is driving these

signals. Active deassertion of these signals occurs only

when the LSI53C895A is in an information transfer

phase. When operating in a differential environment or at

fast SCSI timings, TolerANT Active negation should be

enabled to improve setup and deassertion times. Active

negation is disabled after reset or when this bit is cleared.

For more information on LSI Logic TolerANT technology,

see

Chapter 1, “General Description.”

Note:

Set this bit if the Enable Ultra SCSI bit in

is set.

7

6

5

4

3

2

1

0

TE

STR

HSC

DSI

S16

TTM

CSF

STW

0

0

0

0

x

0

0

0