Scsi transfer (sxfer), Register: 0x05 – Avago Technologies LSI53C895A User Manual

Page 140

4-32

Registers

Register: 0x05

SCSI Transfer (SXFER)

Read/Write

Note:

When using Table Indirect I/O commands, bits [7:0] of this

register are loaded from the I/O data structure.

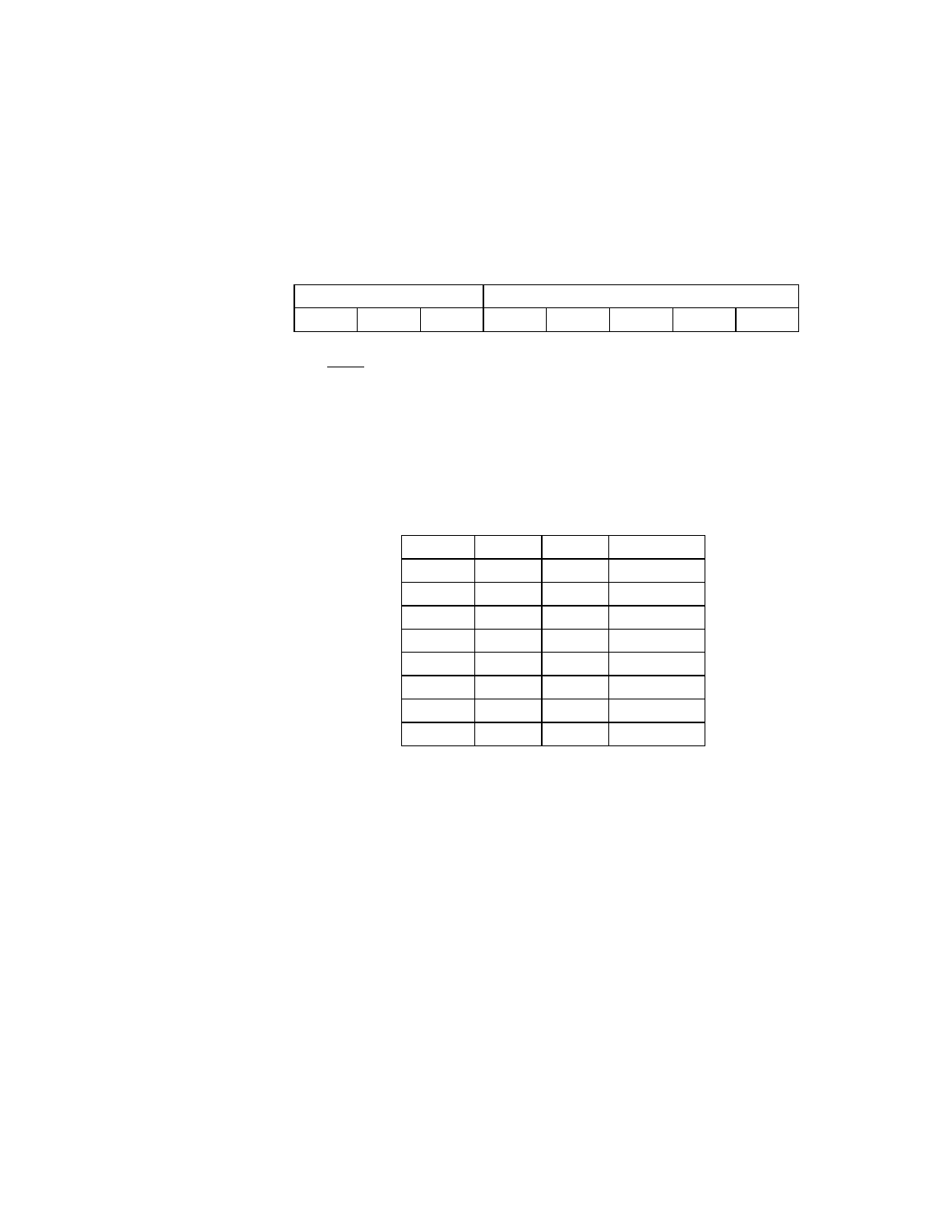

TP[2:0]

SCSI Synchronous Transfer Period

[7:5]

These bits determine the SCSI synchronous transfer

period used by the LSI53C895A when sending

synchronous SCSI data in either the initiator or target

mode. These bits control the programmable dividers in

the chip.

The synchronous transfer period the LSI53C895A should

use when transferring SCSI data is determined in the

following example:

The LSI53C895A is connected to a hard disk which can

transfer data at 10 Mbytes/s synchronously. The

LSI53C895A’s SCLK is running at 40 MHz. The

synchronous transfer period (

) is

found as follows:

SXFERP = Period/SSCP + ExtCC

Period = 1

÷

Frequency = 1

÷

10 Mbytes/s = 100 ns

SSCP = 1

÷

=

SSCF = 1

÷

40 MHz = 25 ns

7

5

4

0

TP[2:0]

MO[4:0]

0

0

0

0

0

0

0

0

TP2

TP1

TP0

XFERP

0

0

0

4

0

0

1

5

0

1

0

6

0

1

1

7

1

0

0

8

1

0

1

9

1

1

0

10

1

1

1

11

- MGA-725M4 (4 pages)

- MGA-71543 (4 pages)

- MGA-71543 (3 pages)

- MGA-82563 (6 pages)

- 3ware 9690SA-8I (Channel) (138 pages)

- 3ware 9690SA-8I (Channel) (380 pages)

- 3ware SAS 9750-8i (48 pages)

- 3ware SAS 9750-8i (29 pages)

- 3ware 9550SXU-8LP (Channel) (149 pages)

- 3ware 9550SXU-8LP (Channel) (40 pages)

- 3ware 9650SE-8LPML (Channel) (45 pages)

- 3ware 9690SA-8I (Channel) (27 pages)

- 3ware 9690SA-8I (Channel) (361 pages)

- 6160 SAS Switch (2 pages)

- Cache Protection for RAID Controller Cards (139 pages)

- Cache Protection for RAID Controller Cards (13 pages)

- MegaRAID SAS 9271-8iCC (13 pages)

- MegaRAID SAS 9361-8i (13 pages)

- MegaRAID SAS 9266-8i (12 pages)

- MegaRAID SAS 9380-8e (43 pages)

- MegaRAID SafeStore Software (502 pages)

- MegaRAID SAS 9285-8ecv (80 pages)

- MegaRAID SAS 9285-8ecv (92 pages)

- MegaRAID SAS 9266-8i (20 pages)

- MegaRAID SAS 9271-8iCC (26 pages)

- MegaRAID SAS 0260CV-4i (49 pages)

- MegaRAID SAS 9271-8i (8 pages)

- MegaRAID SAS 0260CV-4i (72 pages)

- MegaRAID SAS 0260CV-4i (64 pages)

- MegaRAID SAS 9361-8i (7 pages)

- MegaRAID SAS 9341-8i (8 pages)

- MegaRAID SAS 9380-4i4e (7 pages)

- MegaRAID SAS 9380-8e (7 pages)

- MegaRAID SAS 0260CV-4i (28 pages)

- MegaRAID SAS 9240-8i (4 pages)

- MegaRAID SAS 9280-24i4e (14 pages)

- MegaRAID SAS 9280-24i4e (16 pages)

- MegaRAID SAS 9260-16i (12 pages)

- MegaRAID SAS 9280-8e (22 pages)

- MegaRAID SAS 9260-8i (4 pages)

- MegaRAID SafeStore Software (8 pages)

- MegaRAID SAS 9261-8i (4 pages)

- MegaRAID SAS 9285-8e (12 pages)

- MegaRAID SAS 9280-16i4e (12 pages)

- MegaRAID SAS 9280-4i4e (4 pages)