Avago Technologies LSI53C895A User Manual

Page 138

4-30

Registers

Note:

Set this bit to achieve Ultra SCSI transfer rates in legacy

systems that use an 80 MHz clock.

SCF[2:0]

Synchronous Clock Conversion Factor

[6:4]

These bits select a factor by which the frequency of

SCLK is divided before being presented to the

synchronous SCSI control logic. Write these to the same

value as the Clock Conversion Factor bits below unless

fast SCSI operation is desired. See the

register description for examples of how the

SCF bits are used to calculate synchronous transfer

periods. See the table under the description of bits [7:5]

of the SXFER register for the valid combinations.

EWS

Enable Wide SCSI

3

When this bit is clear, all information transfer phases are

assumed to be eight bits, transmitted on SD[7:0]/ and

SDP0/. When this bit is asserted, data transfers are done

16 bits at a time, with the least significant byte on

SD[7:0]/ and SDP0/ and the most significant byte on

SD[15:8]/, SDP1/. Command, Status, and Message

phases are not affected by this bit.

CCF[2:0]

Clock Conversion Factor

[2:0]

These bits select a factor by which the frequency of

SCLK is divided before being presented to the SCSI core.

The synchronous portion of the SCSI core can be run at

a different clock rate for fast SCSI, using the

Synchronous Clock Conversion Factor bits. The bit

encoding is displayed in the table below. All other

combinations are reserved.

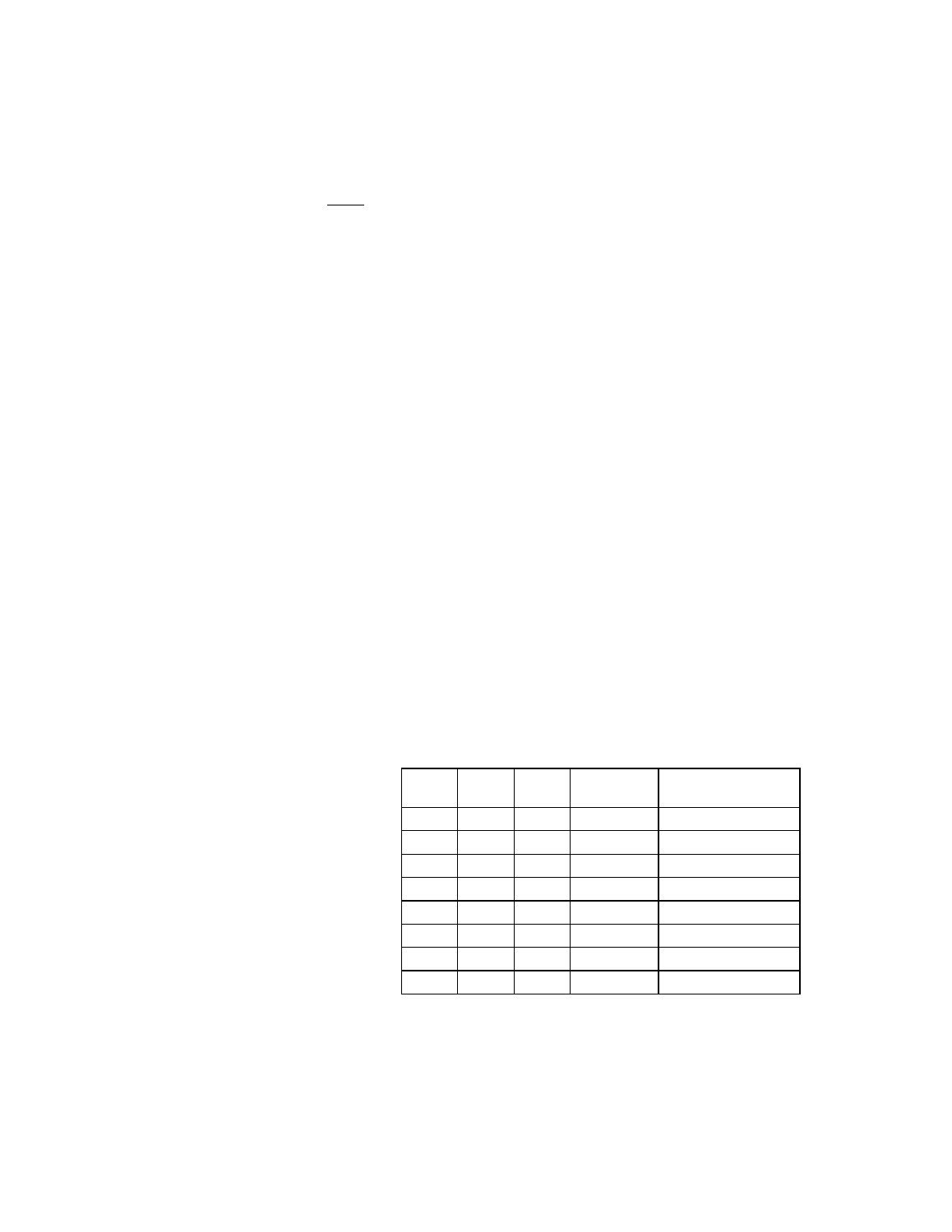

SCF2

CCF2

SCF1

CCF1

SCF0

CCF0

Factor

Frequency

SCSI Clock

(MHz)

0

0

0

SCLK/3

50.01–75.0

0

0

1

SCLK/1

16.67–25.0

0

1

0

SCLK/1.5

25.01–37.5

0

1

1

SCLK/2

37.51–50.0

1

0

0

SCLK/3

50.01–75.0

1

0

1

SCLK/4

75.01–80.00

1

1

0

SCLK/6

120

1

1

1

SCLK/8

160