7 power and ground signals, Table 3.14 power and ground signals, Power and ground signals – Avago Technologies LSI53C895A User Manual

Page 105: Section 3.7, “power and ground signals

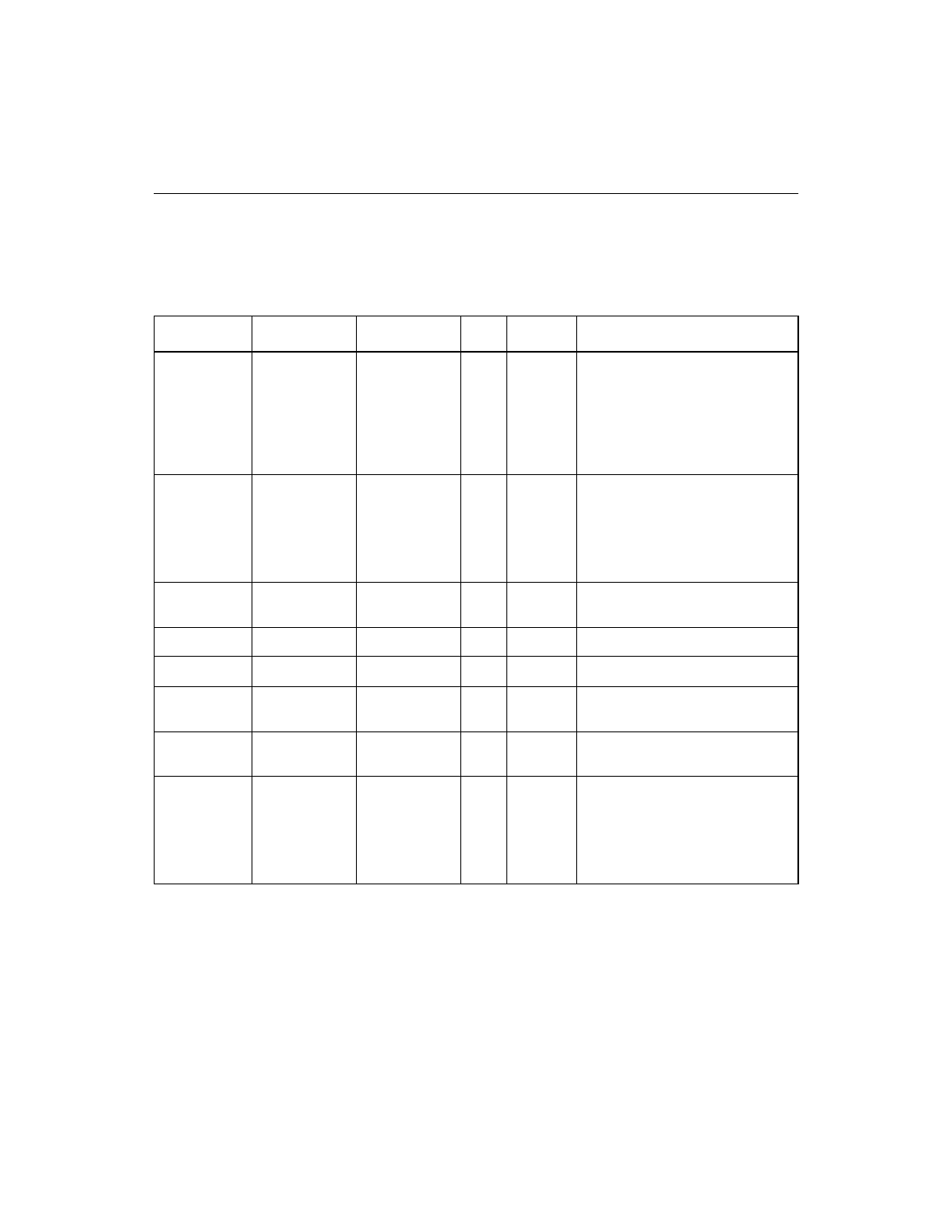

Power and Ground Signals

3-17

3.7 Power and Ground Signals

describes the Power and Ground signals.

Table 3.14

Power and Ground Signals

Name

PQFP

BGA Pos

Type

Strength Description

VSS_I/O

8, 18, 31, 41,

56, 78, 91,

110, 120, 128,

131, 139, 151,

169, 179, 193,

200

A1, D4, D8,

D13, D17, H4,

H17, J9–12,

K9–12, L9–12,

M9–12, N4,

N17, U4, U8,

U13, U17

G

N/A

Ground for PCI bus

drivers/receivers, SCSI bus

drivers/receivers, local memory

interface drivers, and other I/O

pins.

VDD_I/O

2, 13, 23, 26,

36, 46, 60, 73,

81, 86, 96,

115, 125, 134,

144, 164, 174,

184, 197

D6, D11, D15,

F4, F17, K4,

L17, R4, R17,

U6, U10, U15

P

N/A

Power for PCI bus

drivers/receivers, SCSI bus

drivers/receivers, local memory

interface drivers/receivers, and

other I/O pins.

VDD_CORE

64, 190

P1–2, P17,

R19

P

N/A

Power for core logic.

VSS_CORE

68, 187

M3, N18, P20

G

N/A

Ground for core logic.

VSS_CORE2

N1

G

N/A

Ground for core logic.

VDDA

85

H19

P

N/A

Power for analog cells (clock

quadrupler and diffsense logic).

VSSA

83

J18

G

N/A

Ground for analog cells (clock

quadrupler and diffsense logic).

VDD_RBIAS

RBIAS

129

130

A11

A10

I

N/A

Used to connect an external

resistor to generate the bias

current used by LVDlink pads.

Resistor value should be 9.76 k

Ω

.

Connect other end of resistor to

V

DD

.