Lsi53c895a vs. lsi53c895 pin/ball differences – Avago Technologies LSI53C895A User Manual

Page 332

6-72

Electrical Specifications

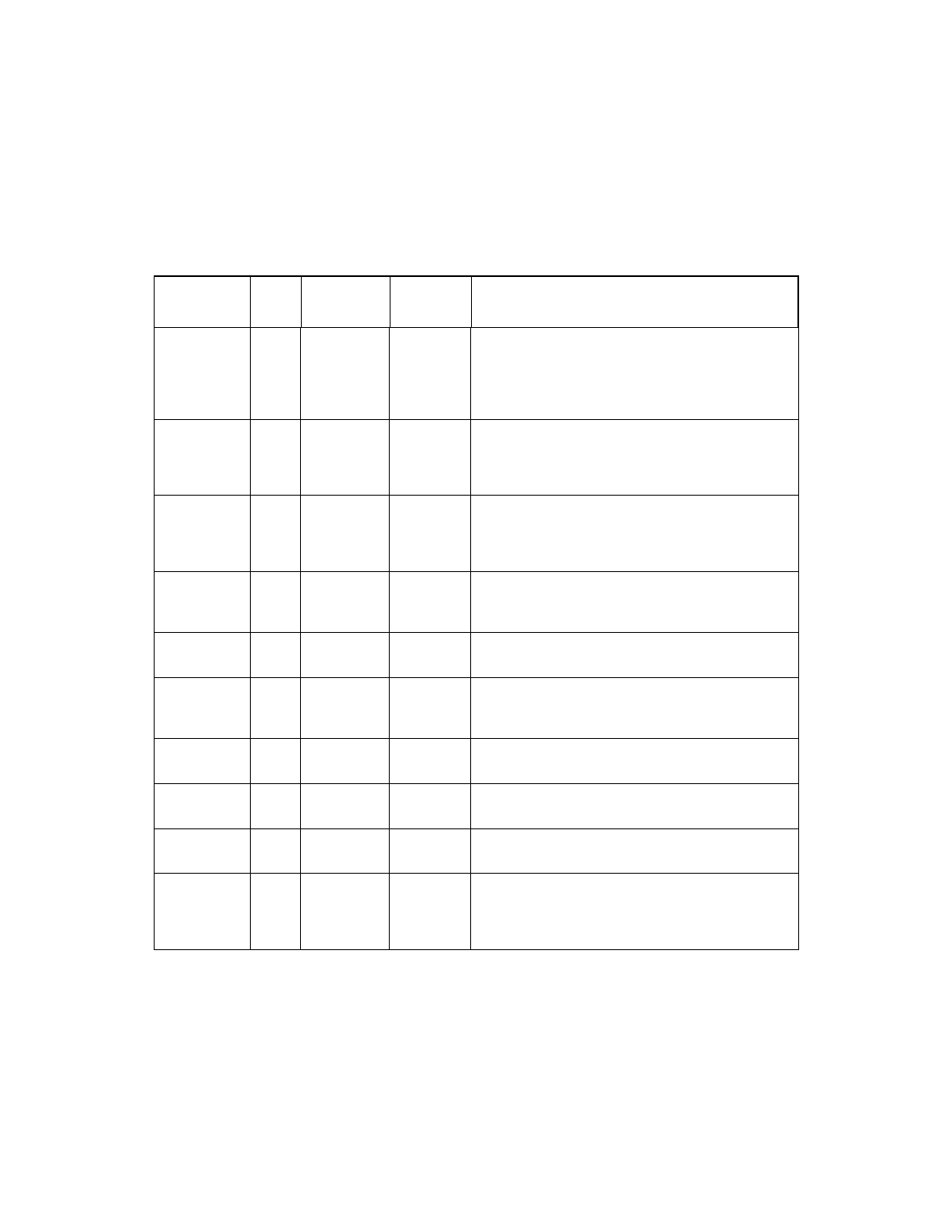

indicates the differences between the LSI53C895A and the

LSI53C895 signal names and locations.

Table 6.54

LSI53C895A vs. LSI53C895 Pin/Ball Differences

Pin/Ball

Name

Type

208 PQFP

Pin #

272 BGA

Ball #

Description

ALT_IRQ/

I/O

1

Y2

Previously NC. Alternate Interrupt Request, when

asserted low, indicates that an interrupting

condition has occurred in the SCSI Function and

that service is required from the host CPU. The

output drive of this pin is open drain.

SREQ2

−

SREQ2+

I/O

I/O

101

102

B20

B19

Previously NC. SREQ2

−

and SREQ2+ are data

handshake lines from target device. They are

duplicates of SREQ

−

and SREQ+ enabled by

pulling MAD5 HIGH at reset.

SACK2

−

SACK2+

I/O

I/O

160

161

D2

D3

Previously NC. SACK2

−

and SACK2+ are data

handshake lines from the initiator device. They are

duplicates of SACK

−

and SACK+ enabled by

pulling MAD5 HIGH at reset.

TEST_RST/

I

178

K2

Previously TESTIN. TEST_RST/ is used for

LSI Logic test purposes only to reset the

LSI53C895A. It should not be driven LOW.

TCK

I

180

K1

Previously TEST. TCK provides the clock for the

JTAG test logic.

TMS

I

181

L1

Previously TEST. TMS is decoded by the TAP

controller and is used to control the JTAG test

operations.

TDO

O

182

L2

Previously TEST. TDO is a serial output used for

test instructions and data from the JTAG test logic.

TDI

I

183

L3

Previously TEST. TDI is a serial input used for test

instructions and data to the JTAG test logic.

TRST/

I

206

Y1

Previously NC. TRST/ provides a reset for the

JTAG test logic.

GPIO5

GPIO6

GPIO7

GPIO8

I/O

I/O

I/O

I/O

52

54

55

205

W19

W20

V19

W2

Previously NC. GPIO[8:5] are SCSI General

Purpose I/O pins. These pins power-up as inputs.