Altera PCI Compiler User Manual

Page 97

Altera Corporation

User Guide Version 11.1

3–23

October 2011

Functional Description

shows definitions for the local target transaction status register

outputs.

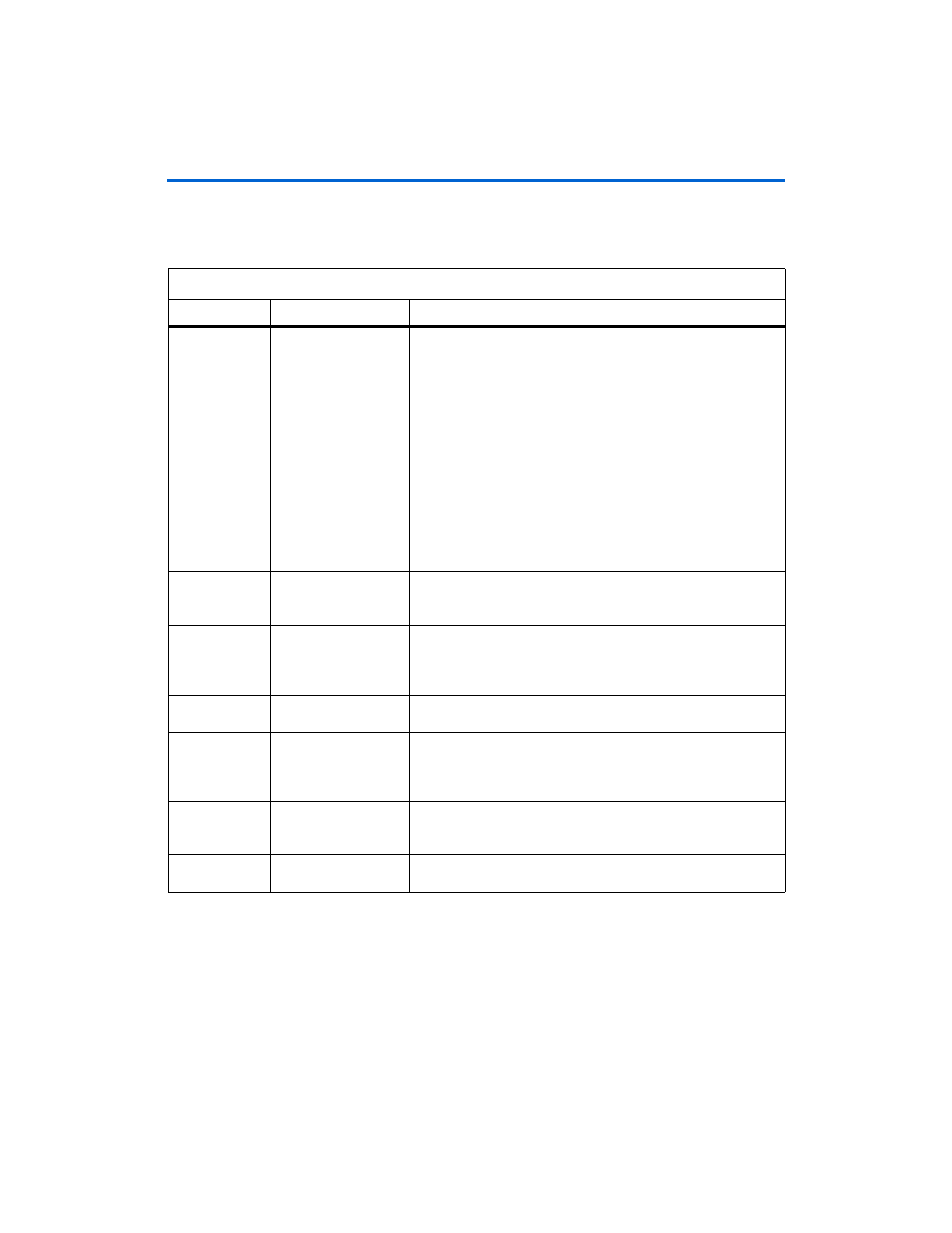

Table 3–8. Local Target Transaction Status Register (lt_tsr[11..0]) Bit Definition

Bit Number

Bit Name

Description

5..0

bar_hit[5..0]

Base address register hit. Asserting

bar_hit[5..0]

indicates

that the PCI address matches that of a base address register and

that the PCI MegaCore function has claimed the transaction. Each

bit in the

bar_hit[5..0]

bus is used for the corresponding base

address register (e.g.,

bar_hit[0]

is used for

BAR0

).

When BAR0 and BAR1 are used to implement a 64-bit base

address register,

bar_hit[0]

and

bar_hit[1]

are asserted to

indicate that the

pci_mt64

and

pci_t64

MegaCore functions

have claimed the transaction.

When BAR1 and BAR2 are used to implement a 64-bit base

address register,

bar_hit[1]

and

bar_hit[2]

are asserted to

indicate that the

pci_mt64

and

pci_t64

MegaCore functions

have claimed the transaction.

6

exp_rom_hit

Expansion ROM register hit. The PCI MegaCore function asserts

this signal when the transaction address matches the address in the

expansion ROM BAR.

7

trans64bit

64-bit target transaction. The

pci_mt64

and

pci_t64

assert this

signal when the current transaction is 64 bits. If a transaction is

active and this signal is low, the current transaction is 32 bits. This

bit is reserved for

pci_mt32

and

pci_t32

.

8

targ_access

Target access. The PCI MegaCore function asserts this signal when

a PCI target access is in progress.

9

burst_trans

Burst transaction. When asserted, this signal indicates that the

current target transaction is a burst. This signal is asserted if the PCI

MegaCore function detects both

framen

and

irdyn

signals

asserted at the same time during the first data phase.

10

pci_xfr

PCI transfer. This signal is asserted to indicate that there was a

successful data transfer on the PCI side during the previous clock

cycle.

11

dac_cyc

Dual address cycle. When asserted, this signal indicates that the

current transaction is using a dual address cycle.