Configuration read transactions – Altera PCI Compiler User Manual

Page 136

3–62

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Target Mode Operation

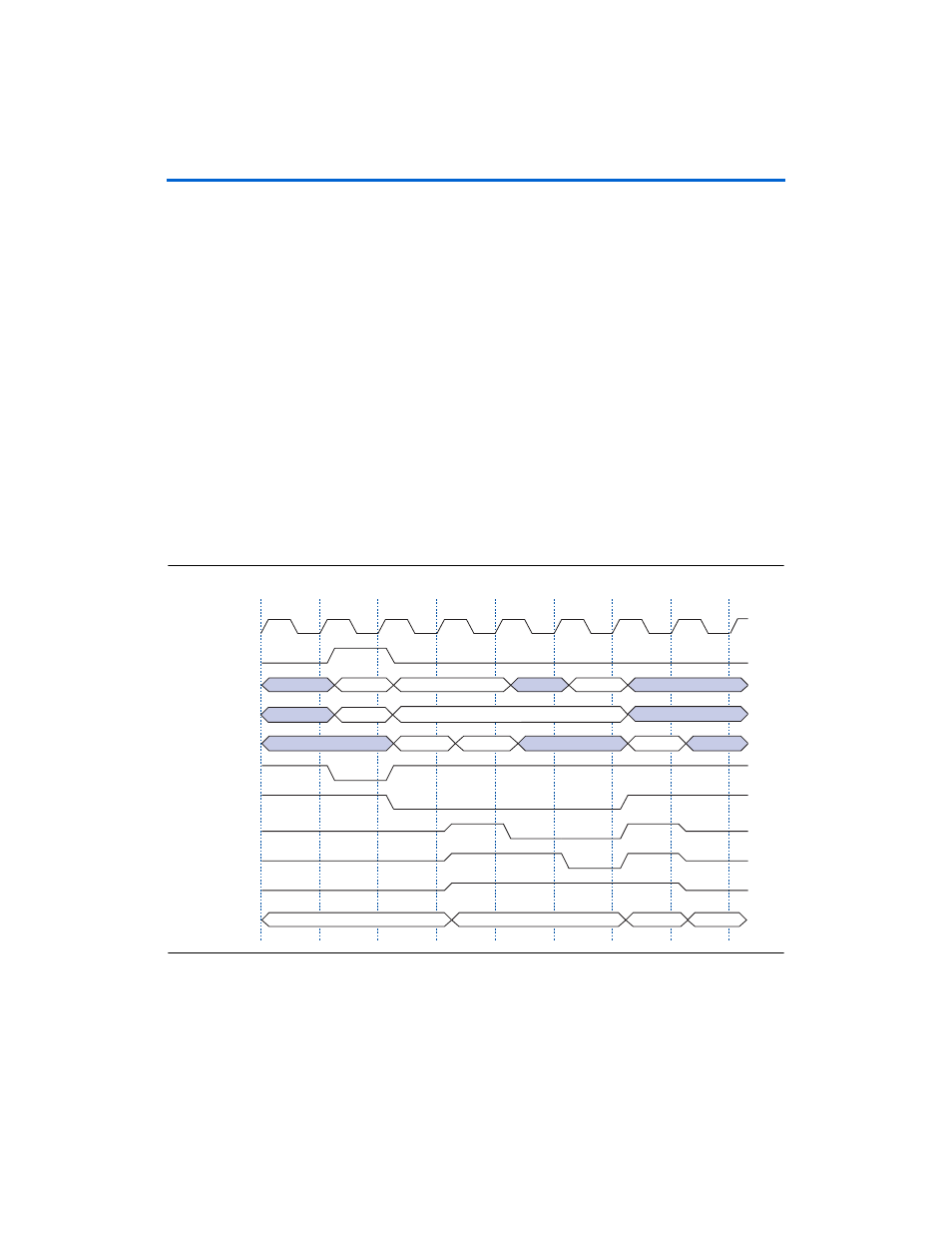

Configuration Read Transactions

Configuration read transactions are 32 bits. Configuration cycles are

automatically handled by the PCI MegaCore functions and do not require

local side actions.

shows a typical configuration read

transaction. This figure applies to all PCI MegaCore functions. The

configuration read transaction is similar to 32-bit single-cycle

transactions, except for the following terms:

■

During the address phase, idsel must be asserted

■

Because the configuration read does not require data from the local

side, the PCI MegaCore functions assert trdyn independent from

the lt_rdyn signal

The second case above results in trdyn being asserted in clock cycle 6

instead of clock cycle 7 as shown in

. The configuration read

cycle ends in clock cycle 8.

1

The local side cannot retry, disconnect, or abort configuration

cycles.

Figure 3–14. Configuration Read Transaction

ad[31..0]

cben[3..0]

par

framen

irdyn

devseln

trdyn

stopn

clk

lt_tsr[11..0]

Adr

A

Adr-PAR

Z

BE0_L

Z

000

100

D0-L-PAR

000

500

D0_L

idsel

1

2

3

4

5

6

7

8