Pci master operation, Pci master operation –27, Figure 7–8 – Altera PCI Compiler User Manual

Page 295

Altera Corporation

User Guide Version 11.1

7–27

October 2011

Functional Description

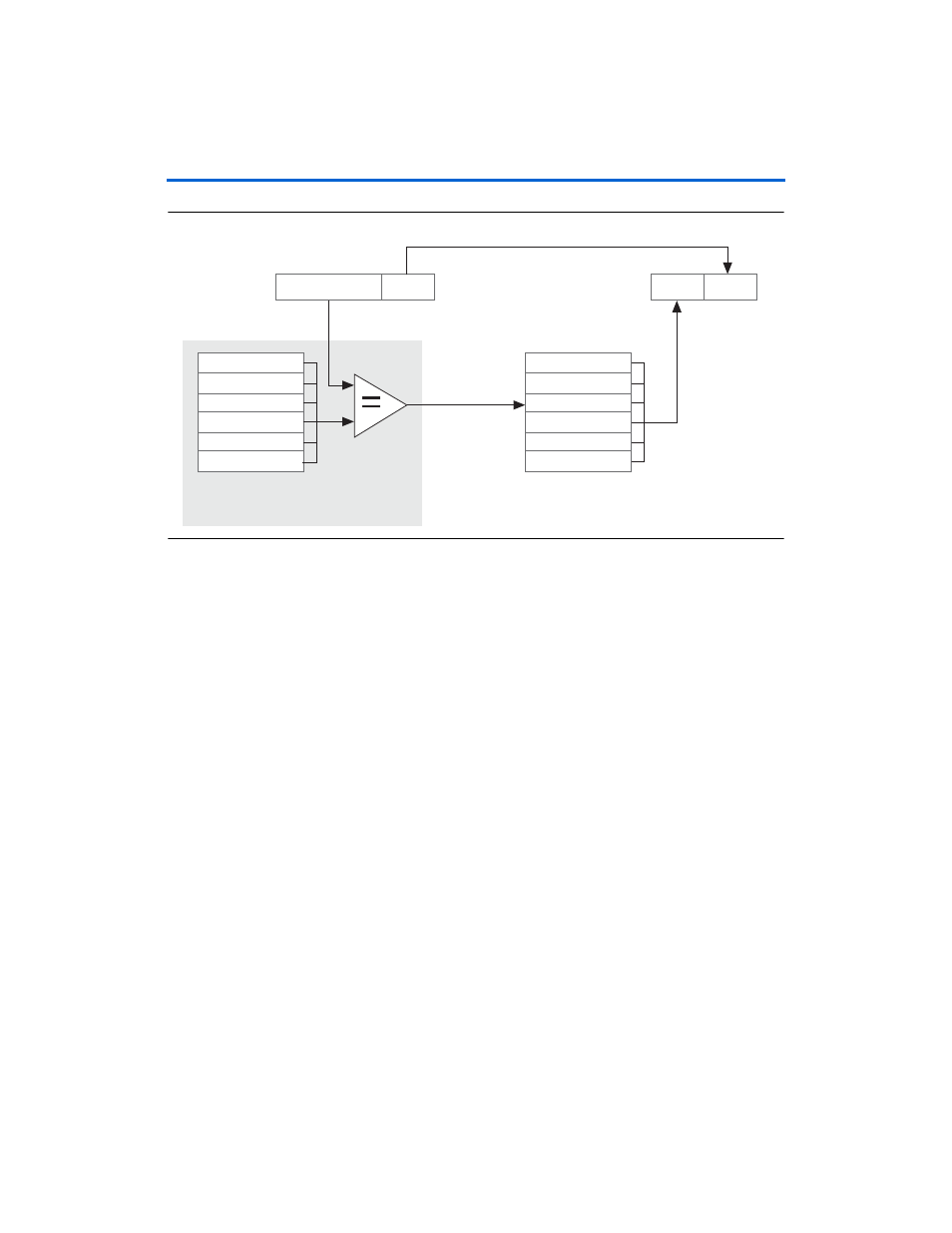

Figure 7–8. PCI-to-Avalon Address Translation

PCI Master

Operation

This section describes the PCI master mode operation. Because the PCI

Target-Only Peripheral mode is a subset of the PCI Master/Target

Peripheral mode, the information in the previous section also applies to

the target side of the PCI Master/Target Peripheral mode.

The PCI master mode operation applies to Avalon-to-PCI transactions.

The PCI-Avalon bridge automatically accepts Avalon-MM read and

write operations targeting the PCI Bus Access Slave port interface and

translates them into PCI master transactions. Transaction progress and

error conditions are stored in the control/status registers that can be

accessed via the control access port.

The Avalon-to-PCI address translation module (refer to

Address Translation” on page 7–35

) controls whether Avalon-MM read

and write requests are issued on PCI as memory, I/O, or configuration

space transactions. Except for the command used, accesses to the

different spaces operate identically. Burst transactions may even be

attempted to configuration space, but this is unusual behavior and target

devices may not operate correctly.

You have the option to make the Avalon-to-PCI address translation

module either fixed at compile time or dynamically-configured at run

time. A fixed Avalon-to-PCI address translation module is very useful for

embedded systems with very few PCI devices. If the dynamic address

translation table is used, you need to write to it using the Control

Register Access Avalon Slave

port.

Avalon_Addr_B0

Avalon Address

PCI Address

High

Low

Hardcoded BAR Specific

Avalon Addresses

Matched BAR

Selects Avalon

Addresses

Inside PCI MegaCore Function

BAR Specific Number

of High Avalon Bits

N = Number of Pass Through Bits (BAR Specific)

M = Number of Avalon Address Bits

P = Number of PCI Address Bits (64/32)

Low Address Bits Unchanged

(BAR Specific Number of Bits)

Avalon_Addr_B1

Avalon_Addr_B2

Avalon_Addr_B3

Avalon_Addr_B4

Avalon_Addr_B5

0

N-1

M-1

N

High

Low

0

P-1

N N-1

BAR0 (or 0:1)

BAR1

BAR2

BAR3

BAR4

BAR5