Table 4–3, Contains – Altera PCI Compiler User Manual

Page 215

Altera Corporation

User Guide Version 11.1

4–5

October 2011

PCI Compiler

Testbench

Refer to

“Simulation Flow” on page 4–20

for more information on the

modified testbench files.

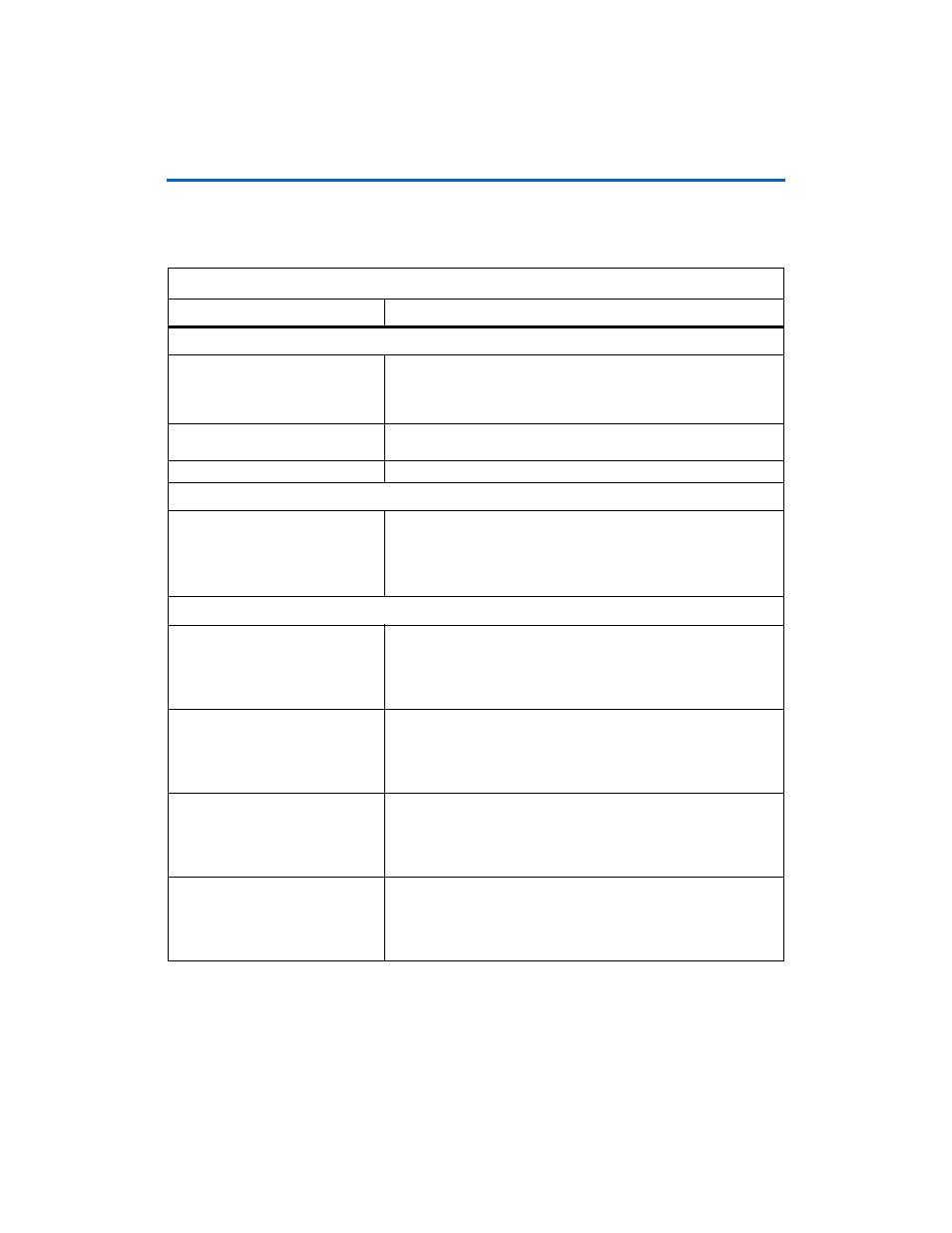

Table 4–3. Files Contained in the example Directory

File

Description

Modified Testbench Files

mstr_tranx

This module contains the master transactor code. The INITIALIZATION

section has the parameters set to simulate the Local Reference Design.

The USER COMMANDS section has the PCI commands that will be

executed during simulation.

This module contains the target transactor code. The address_lines and

mem_hit_range settings are set to simulate the reference design.

trgt_tranx_mem_init.dat

This file is the memory initialization file for the target transactor.

Top-level Design File

This top-level file instantiates the testbench module files, the

IP functional simulation model of the

pci_mt64

MegaCore function,

and the reference design file. The

idsel

signal of the Altera PCI

MegaCore function is connected to address bit 28 and the

idsel

signal

of the target transactor is connected to address bit 29.

Simulation Scripts

run_altera_modelsim.tcl

This script can be used with the Altera-ModelSim simulator. This script

compiles all the files provided in <path>\pci_compiler

\megawizard_flow\testbench\<HDL language>

\<PCI MegaCore function>\example and simulates the reference

design for the transactions specified in the mstr_tranx file.

run_modelsim.tcl

This script can be used with the ModelSim SE, PE or AE simulators.

This script compiles all the files provided in <path>\pci_compiler

\megawizard_flow\testbench\<HDL language>

\<PCI MegaCore function>\example and simulates the reference

design for the transactions specified in the mstr_tranx file.

run_vcs.sh

This script is used with VCS simulator. This script compiles the files

provided in <path>\pci_compiler\megawizard_flow

\testbench\<HDL language>\<PCI MegaCore function>

\example\<function> and simulates the reference design for the

transactions specified in the mstr_tranx file.

run_ncverilog.sh

This script must be used with NC-Verilog simulator. This script will

compile all the files provided in <path>\pci_compiler

\megawizard_flow\testbench\<HDL language>

\<PCI MegaCore function>\example and simulates the reference

design for the transactions specified in the mstr_tranx file.

Note to

(1)

This file is provided in both VHDL and Verilog HDL.