Target transactor (trgt_tranx) – Altera PCI Compiler User Manual

Page 342

8–12

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Testbench Specifications

Target Transactor (trgt_tranx)

The testbench target transactor simulates the behavior of a target agent on

the PCI bus. The master transactions initiated by the Altera PCI

MegaCore function under test should be addressed to the target

transactor. The target transactor operates in 32- or 64-bit mode. The target

transactor implements two base address registers BAR0 and BAR1. Refer

to

The base address registers define the target transactor address space.

Refer to

.

The memory range reserved by BAR0 is defined by the address_lines

and mem_hit_range settings in the target transactor source code.

The target transactor has a 32-bit register that stores data for I/O

transactions. This register is mapped to BAR1 of the configuration

address space. Because this is the only register that is mapped to BAR1,

any address that is within the BAR1 range results in an io_hit action.

Refer to the target transactor source code to see how the address is

decoded for io_hit.

1

The target transactor ignores byte enables for all memory, I/O,

and configuration transactions.

The target transactor idsel signal should be connected to one of the PCI

address bits in the top-level file of the PCI testbench for configuration

transactions to occur on BAR0 and BAR1.

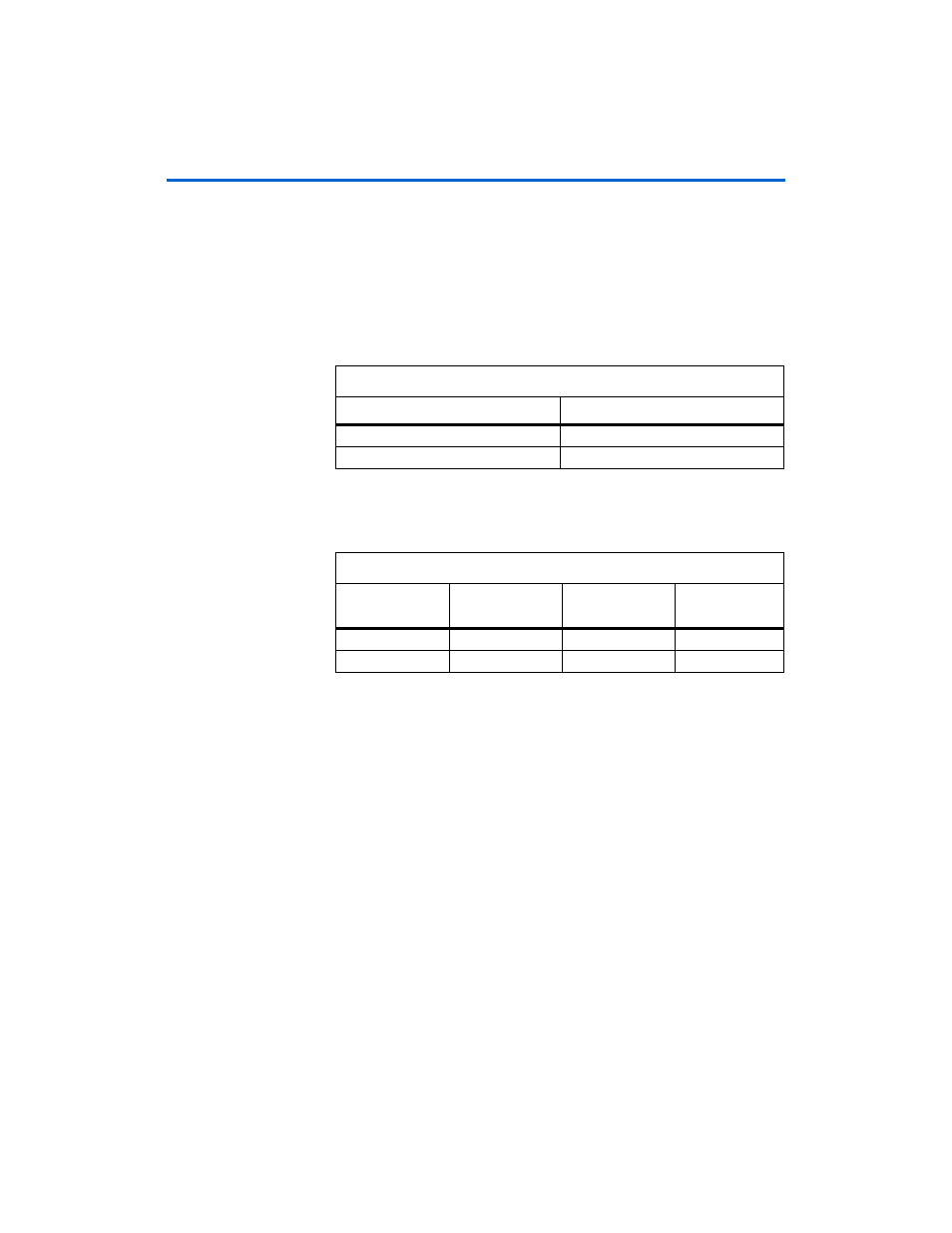

Table 8–5. Target Transactor Configuration Address Space

Configuration Register

Configuration Address Offset

BAR0

x10

BAR1

x14

Table 8–6. Target Transactor Address Space Allocation

Configuration

Register

Address Space

Type

Block Size

Address Offset

BAR0

Memory Mapped

1 KByte

000-3FF

BAR1

I/O Mapped

16 Bytes

0-F