Altera PCI Compiler User Manual

Page 26

14

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Performance and Resource Utilization

lists memory utilization and performance data for Stratix II

devices.

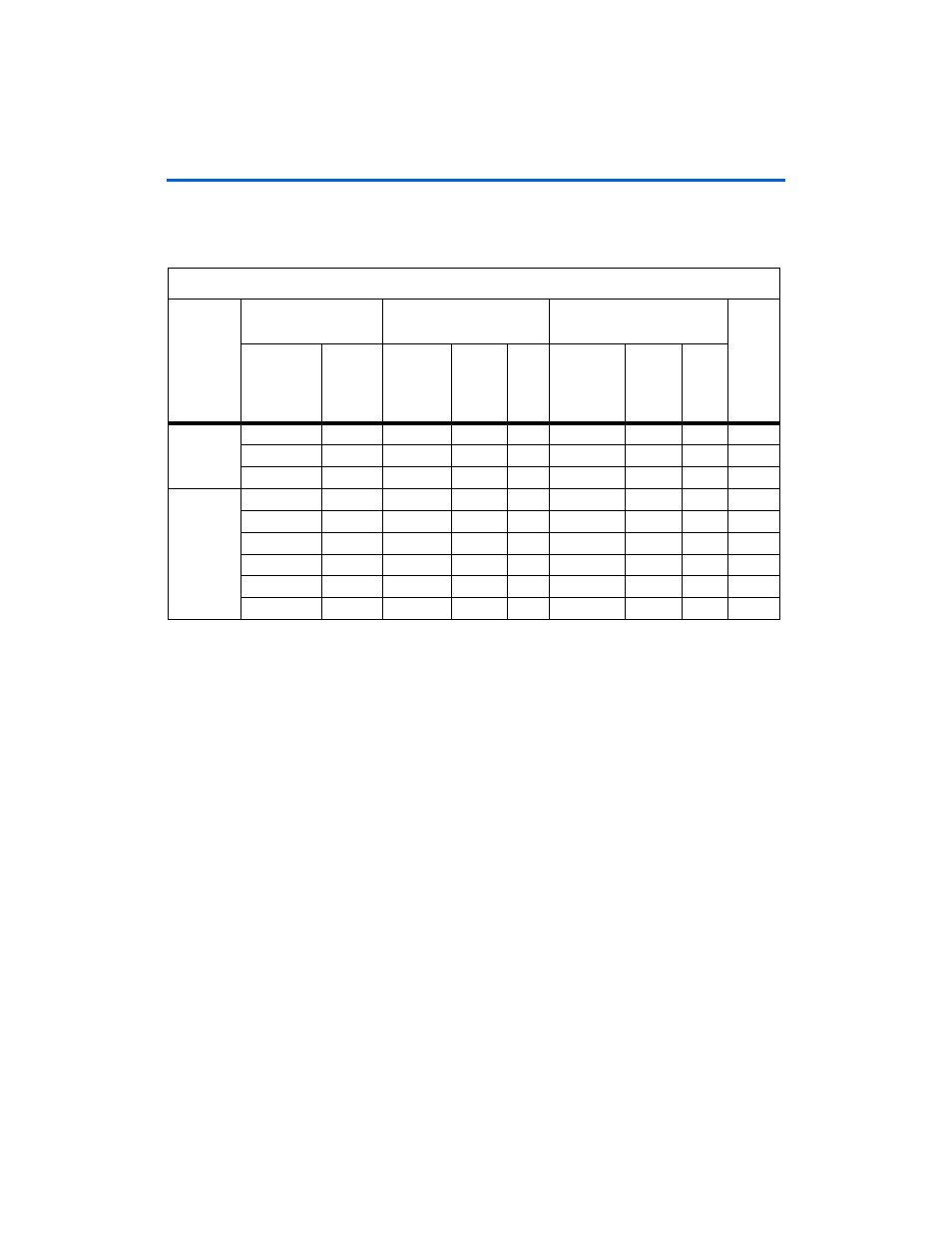

Table 8. Memory Utilization & Performance Data for Stratix II Devices

PCI

Device

Mode

Performance Setting

32-Bit PCI Interface

64-Bit PCI Interface

PCI

f

MAX

(MHz)

PCI Target

PCI

Master

Utilization

ALUTs

M4K

Memory

Blocks

I/O

Pins

Utilization

ALUTs

M4K

Memory

Blocks

I/O

Pins

PCI

Target-

Only

Min

N/A

543

0

48

767

0

87

>67

Typical

N/A

886

4

48

1,165

6

87

>67

Max

N/A

1,240

4

48

1,556

68

87

>67

PCI

Master/

Target

Min

Typical

1,726

6

50

2,393

9

89

>67

Typical

Typical

1,953

8

50

2,729

123

89

>67

Max

Typical

2,321

8

50

3,114

12

89

>67

Min

Max

2,532

9

50

3,665

15

89

>67

Typical

Max

2,753

11

50

3,989

18

89

>67

Max

Max

3,149

11

50

4,350

18

89

>67

Notes to

(1)

Min

= Single-cycle transactions

Typical

= Burst transactions with a single pending read

Max

= Burst transactions with multiple pending reads

(2)

The LE count for Stratix II devices is based on the number of adaptive look-up tables (ALUTs) used for the design as

reported by the Quartus II software.

(3)

In some compilations one M512 block was used, but it is not counted.

(4)

The data was obtained by performing compilations on a Stratix II EP2S60F1020C5 device. Each of the device types

was parameterized to use one BAR that reserved 1 MByte of memory on the Avalon-MM side. For the PCI

Master/Target Peripheral mode, one MByte of memory was reserved on the PCI side.