Target device signals & signal assertion – Altera PCI Compiler User Manual

Page 80

3–6

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Functional Overview

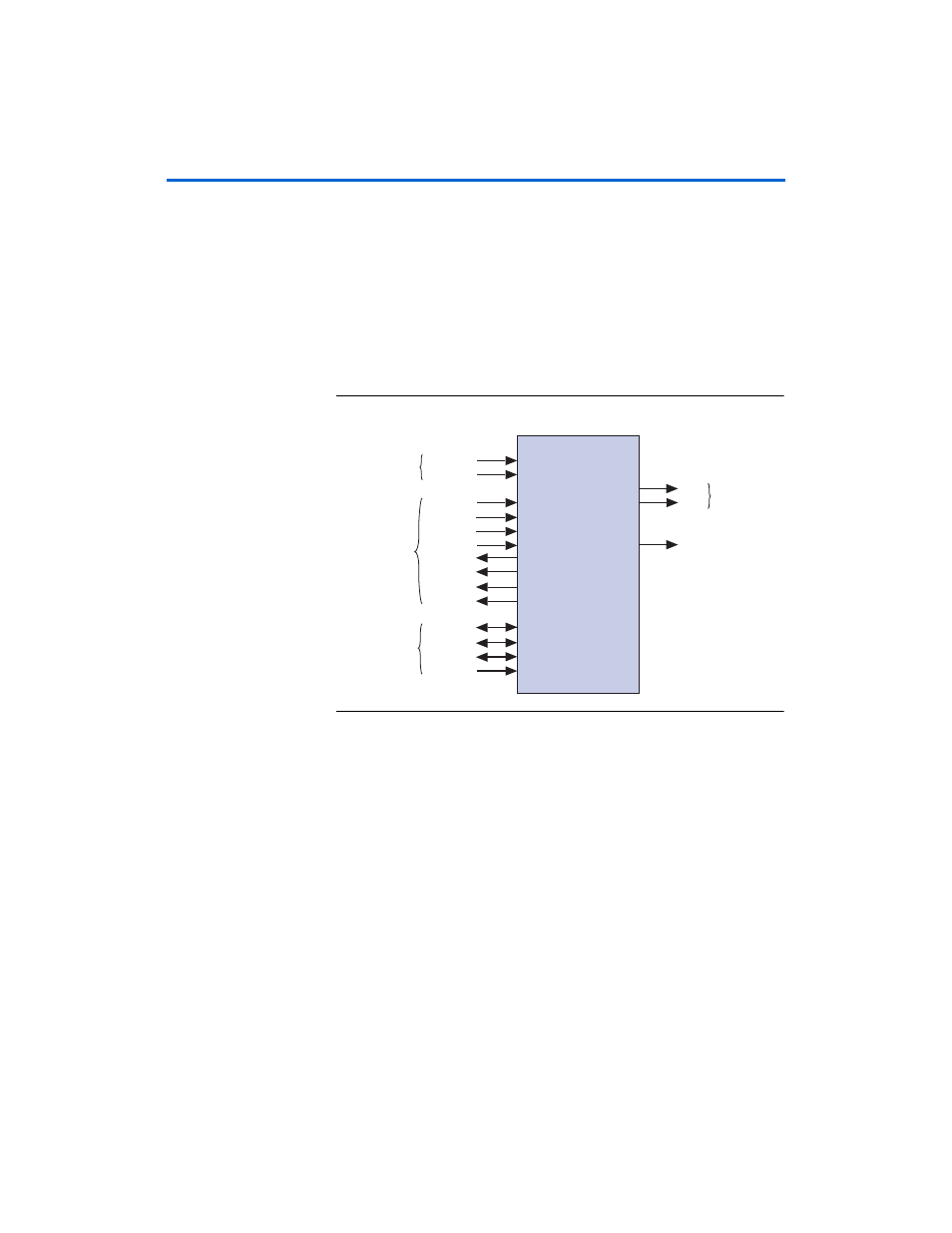

Target Device Signals & Signal Assertion

illustrates the signal directions for a PCI device connecting to

the PCI bus in target mode. These signals apply to the pci_mt64,

pci_t64

, pci_mt32, and pci_t32 functions when they are operating

in target mode. The signals are grouped by functionality, and signal

directions are illustrated from the perspective of the PCI MegaCore

function operating as a target on the PCI bus. The 64-bit extension signals,

including req64n, ack64n, par64, ad[63..32], and cben[7..4],

are not implemented in the pci_mt32 and pci_t32 functions.

Figure 3–5. Target Device Signals

A 32-bit target sequence begins when the PCI master device asserts

framen

and drives the address and the command on the PCI bus. If the

address matches one of the base address registers (BARs) in the PCI

MegaCore function, it asserts devseln to claim the transaction. The

master then asserts irdyn to indicate to the target device for a read

operation that the master device can complete a data transfer, and for a

write operation that valid data is on the ad[31..0] bus.

The PCI MegaCore function drives the control signals devseln, trdyn,

and stopn to indicate one of the following conditions to the PCI master:

■

The PCI MegaCore function has decoded a valid address for one of

its BARs and it accepts the transactions (assert devseln)

■

The PCI MegaCore function is ready for the data transfer (assert

trdyn

)

Target Device

clk

rstn

idsel

req64n

framen

irdyn

trdyn

stopn

devseln

ack64n

par64

par

ad[63..0]

cben[7..0]

perrn

serrn

intan

System

Signals

Interface

Control

Signals

Address,

Data &

Command

Signals

Error

Reporting

Signals

Interrupt

Request

Signal