Control/status register module, Mailbox registers, Pci megacore function – Altera PCI Compiler User Manual

Page 273

Altera Corporation

User Guide Version 11.1

7–5

October 2011

Functional Description

bridge’s master ports must be connected to this port. There is no internal

access inside the bridge from the PCI bus to these registers. You can only

read-from and write-to these registers from the interconnect.

Control/Status Register Module

The PCI-Avalon bridge provides a rich set of control and status registers

including mailbox registers. To access these registers, you must enable

the Control Register Access Avalon Slave port.

Mailbox Registers

The PCI-Avalon bridge provides two sets of mailbox registers. These

registers enable PCI and Avalon-MM masters to pass one DWORD of data

and assert an interrupt. To use the mailbox registers, you must enable the

Control Register Access Avalon Slave

port.

One set of mailbox registers is used by external PCI masters. When a PCI

master writes a 32-bit value to a mailbox register, an Avalon-MM

interrupt is asserted. The number of available mailbox registers is

determined by the PCI-to-Avalon performance profile.

The second set of mailbox registers is used by Avalon-MM masters. When

an Avalon-MM master writes a 32-bit value to an Avalon-PCI mailbox

register, a PCI interrupt is generated. The number of Avalon-PCI mailbox

registers depends on the target performance profile. Refer to

PCI MegaCore Function

The PCI-Avalon bridge instantiates the appropriate PCI MegaCore

function per user specifications. For example, if you select 64 Bit PCI Bus

from the PCI Data Bus Width field (System Options - 2 tab), your system

will use a 64-bit MegaCore function. Refer to

1

To use the PCI-Avalon bridge you must license one of the Altera

PCI MegaCore functions.

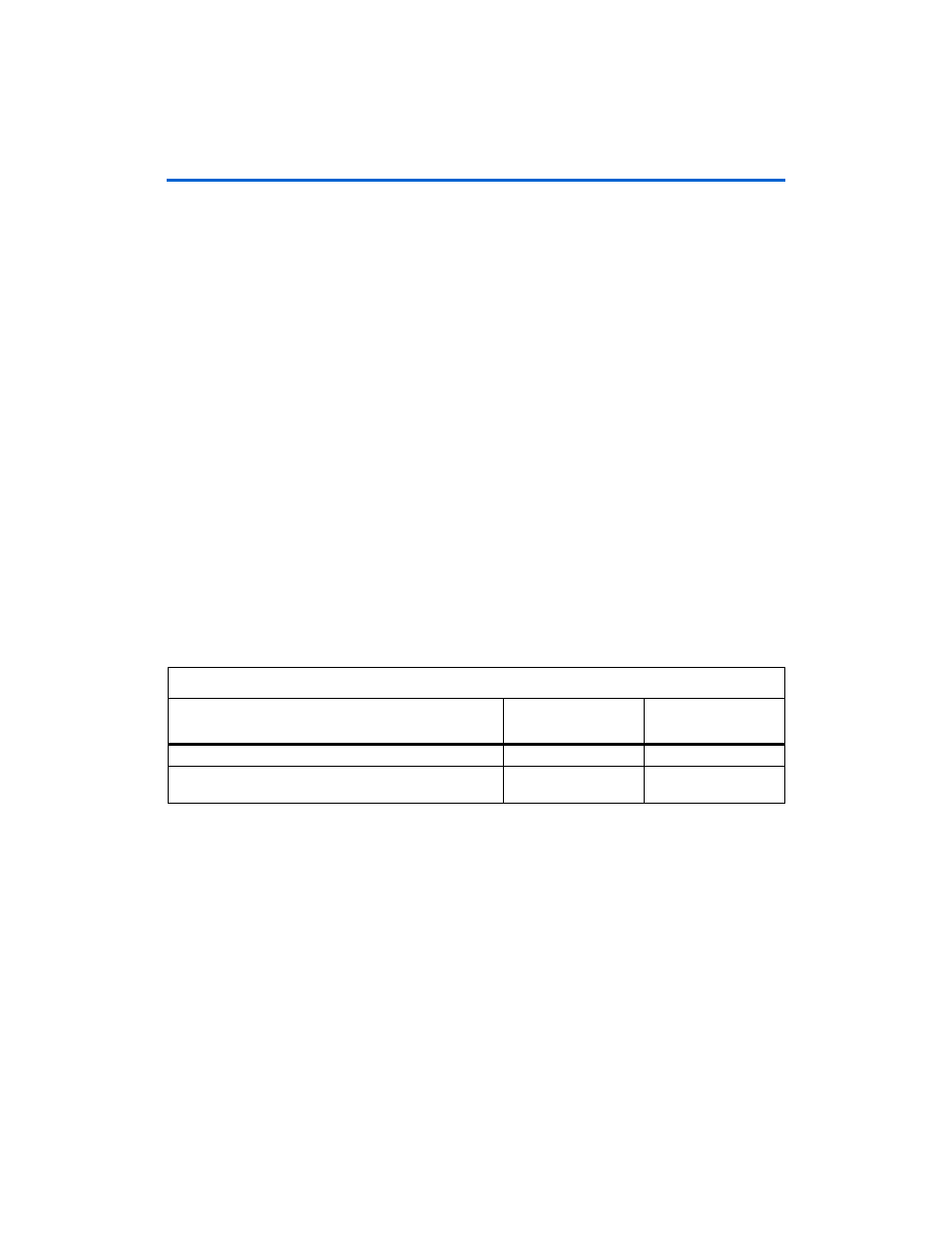

Table 7–1. Target Performance Profiles & Mailbox Registers Used

Target Performance Profile

Number of PCI-Avalon

Mailbox Registers

Number of Avalon-PCI

Mailbox Registers

Single-Cycle Transfers Only

1

1

Burst Transfers with Single Pending Read or Burst

Transfers with Multiple Pending Reads

8

8