Altera PCI Compiler User Manual

Page 185

Altera Corporation

User Guide Version 11.1

3–111

October 2011

Functional Description

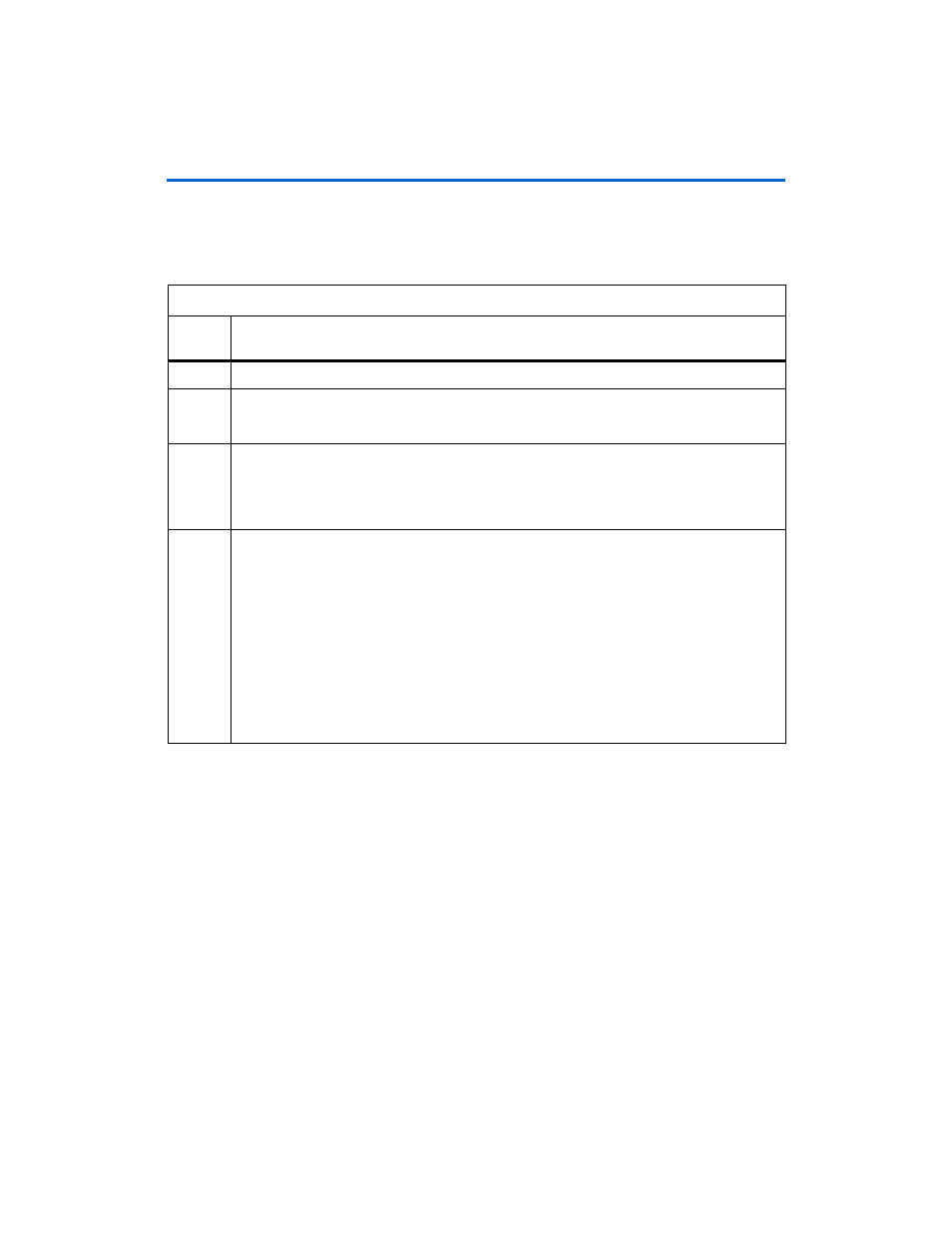

shows the sequence of events for a 64-bit zero-wait state burst

memory write master transaction. The 64-bit extension signals are not

applicable to the pci_mt32 function.

Table 3–39. Zero-Wait State Burst Memory Write Master Transaction (Part 1 of 3)

Clock

Cycle

Event

1

The local side asserts

lm_req64n

to request a 64-bit transaction.

2

The function outputs

reqn

to the PCI bus arbiter to request bus ownership. At the same time, the

function asserts

lm_tsr[0]

to indicate to the local side that the master is requesting control of the

PCI bus.

3

The PCI bus arbiter asserts

gntn

to grant the PCI bus to the function. Although

shows

that the grant occurs immediately and the PCI bus is idle at the time gntn is asserted, this action

may not occur immediately in a real transaction. Before the function proceeds, it waits for

gntn

to be

asserted and the PCI bus to be idle. A PCI bus idle state occurs when both

framen

and

irdyn

are

deasserted.

5

The function turns on its output drivers, getting ready to begin the address phase.

The function also outputs

lm_adr_ackn

to indicate to the local side that it has acknowledged its

request. During this same clock cycle, the local side should provide the PCI address on

l_adi[31..0]

and the PCI command on

l_cbeni[3..0]

.

The local side master interface asserts

lm_rdyn

to indicate that it is ready to send data to the PCI

side. The function does not assert

irdyn

regardless if the local side asserts

lm_rdyn

to indicate

that it is ready to send data, only for the first data phase on the local side. For subsequent data

phases, the PCI MegaCore function asserts

irdyn

if the local side is ready to send data.

The PCI MegaCore function continues to assert its

reqn

signal until the end of the address phase.

The function also asserts

lm_tsr[1]

to indicate to the local side that the PCI bus has been granted.