Altera PCI Compiler User Manual

Page 24

12

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Performance and Resource Utilization

MegaCore function. Using different parameter options may result in

additional logic generated within the function. Results were generated

using the Quartus II software version 11.1.

shows PCI MegaCore function resource utilization and

performance data for Stratix II devices.

shows PCI MegaCore function resource utilization and

performance for Stratix, Stratix GX, and Cyclone devices.

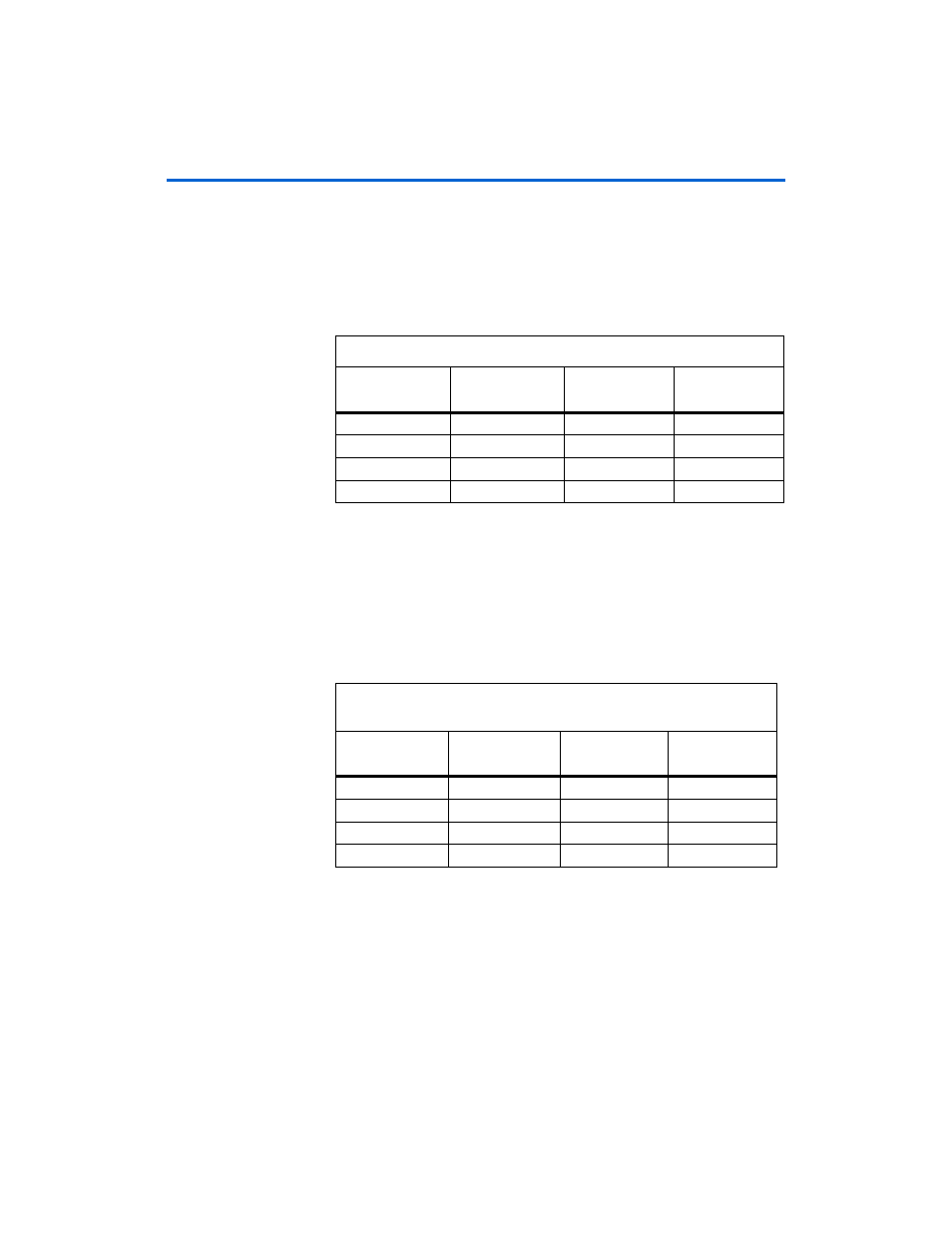

Table 4. PCI MegaCore Function Performance in Stratix II Devices

PCI Function

Utilization

(ALUTs)

I/O Pins

f

MAX

(MHz)

pci_mt64

1,083

89

> 67

pci_t64

714

87

> 67

pci_mt32

754

50

> 67

pci_t32

448

48

> 67

:

(1)

This data was obtained by compiling each of the PCI MegaCore functions

(parameterized to use one BAR that reserves 1 MByte of memory) in the Stratix II

EP2S60F1020C5 device.

(2)

The Utilization for Stratix II devices is based on the number of adaptive look-up

tables (ALUTs) used for the design as reported by the Quartus II software.

Table 5. PCI MegaCore Function Performance in Stratix, Stratix GX &

Cyclone Devices

PCI Function

Logic Elements

(LEs)

I/O Pins

f

MAX

(MHz)

pci_mt64

1,378

89

> 67

pci_t64

966

87

> 67

pci_mt32

1007

50

> 67

pci_t32

661

48

> 67

Note to

(1)

The PCI MegaCore functions use approximately the same number of LEs for the

Stratix, Stratix GX, and Cyclone device families. This data was obtained by

compiling each of the PCI MegaCore functions (parameterized to use one BAR

that reserves 1 MByte of memory) in the Stratix EP1S60F1020C6 device.