Table 3–6 – Altera PCI Compiler User Manual

Page 91

Altera Corporation

User Guide Version 11.1

3–17

October 2011

Functional Description

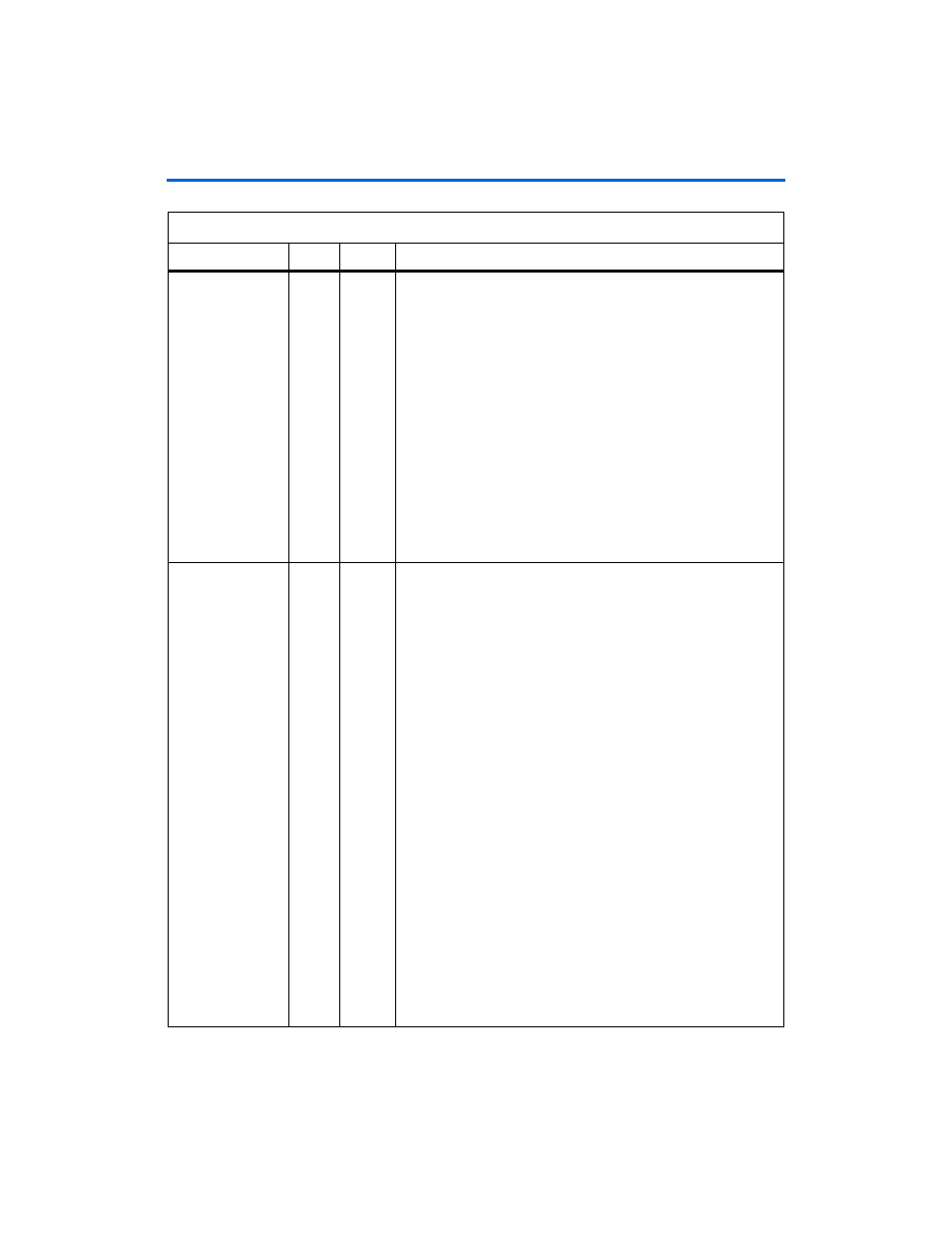

Table 3–6. PCI Local Address, Data, Command & Byte Enable Signals (Part 1 of 3)

Name

Type

Polarity

Description

l_adi[63..0]

Input

–

Local address/data input. This bus is a local-side time multiplexed

address/data bus. This bus changes operation depending on the

function you are using and the type of transaction.

During master transactions, the local side must provide the address

on

l_adi[63..0]

when

lm_adr_ackn

is asserted. For 32-bit

addressing, only the

l_adi[31..0]

signals are valid during the

address phase.

The

l_adi[63..0]

bus is driven active by the local-side logic

during PCI bus-initiated target read transactions or local-side initiated

master write transactions. For

pci_mt32

and

pci_t32

, only

l_adi[31..0]

is used.

For the

pci_mt64

and

pci_t64

functions, the entire

l_adi[63..0]

bus is used to transfer data from the local side

during 64-bit master write and 64-bit and 32-bit target read

transactions.

l_cbeni[7..0]

Input

–

Local command/byte enable input. This bus is a local-side time

multiplexed command/byte enable bus. During master transactions,

the local side must provide the command on

l_cbeni[3..0]

when

lm_adr_ackn

is asserted. For 64-bit addressing, the local side must

provide the DAC command (

B"1101"

) on

l_cbeni[3..0]

and the

transaction command on

l_cbeni[7..4]

when

lm_tsr[1]

is

asserted. The local side must provide the command with the same

encoding as specified in the PCI Local Bus Specification,

Revision 3.0.

The local-master device drives byte enables on the

l_cbeni[7..0]

bus during master transactions. The local master

device must provide the byte-enable value on

l_cbeni[7..0]

during the next clock cycle after

lm_adr_ackn

is asserted. This is

the same clock cycle that immediately follows a local side address

phase.The PCI MegaCore functions drive the byte-enable value from

the local side to the PCI side. The PCI MegaCore function maintains

the same byte enables that were provided with the initial data word on

the local side throughout the burst transaction.

The PCI MegaCore function allows variable byte enable values from

the local side to the PCI side if Allow Variable Byte Enables During

Burst Transaction is turned on in the Parameterize - PCI Compiler

wizard. Refer to

“Advanced PCI MegaCore Function Features” on

for more information.

In

pci_mt32

, only

l_cbeni[3..0]

is implemented. Additionally,

in

pci_mt64

, only

l_cbeni[3..0]

is used when a 32-bit master

transaction is initiated.