Pci interrupt status register – Altera PCI Compiler User Manual

Page 317

Altera Corporation

User Guide Version 11.1

7–49

October 2011

Functional Description

shows the complete map of registers.

The following sections describe the control and status registers in detail.

In describing the register’s bits, the following nomenclature is used:

■

RO: Read only bit. The value of RO bits cannot be modified, but can

be read.

■

RW: Read and write. The value of RW bits can be read and written.

■

RW1C: Read and write "1" to clear. The RW1C bits can be read, but

can only be cleared by writing a 1 to the bit location.

PCI Interrupt Status Register

The PCI interrupt status register contains the status of various events in

the PCI-Avalon bridge logic and allows PCI interrupts to be signaled if

the indicated status bit is set while the corresponding bit in the PCI

interrupt enable register is also set. This register is intended to be accessed

only by other PCI masters; however, there is nothing in the hardware that

prevents other Avalon-MM masters from accessing it.

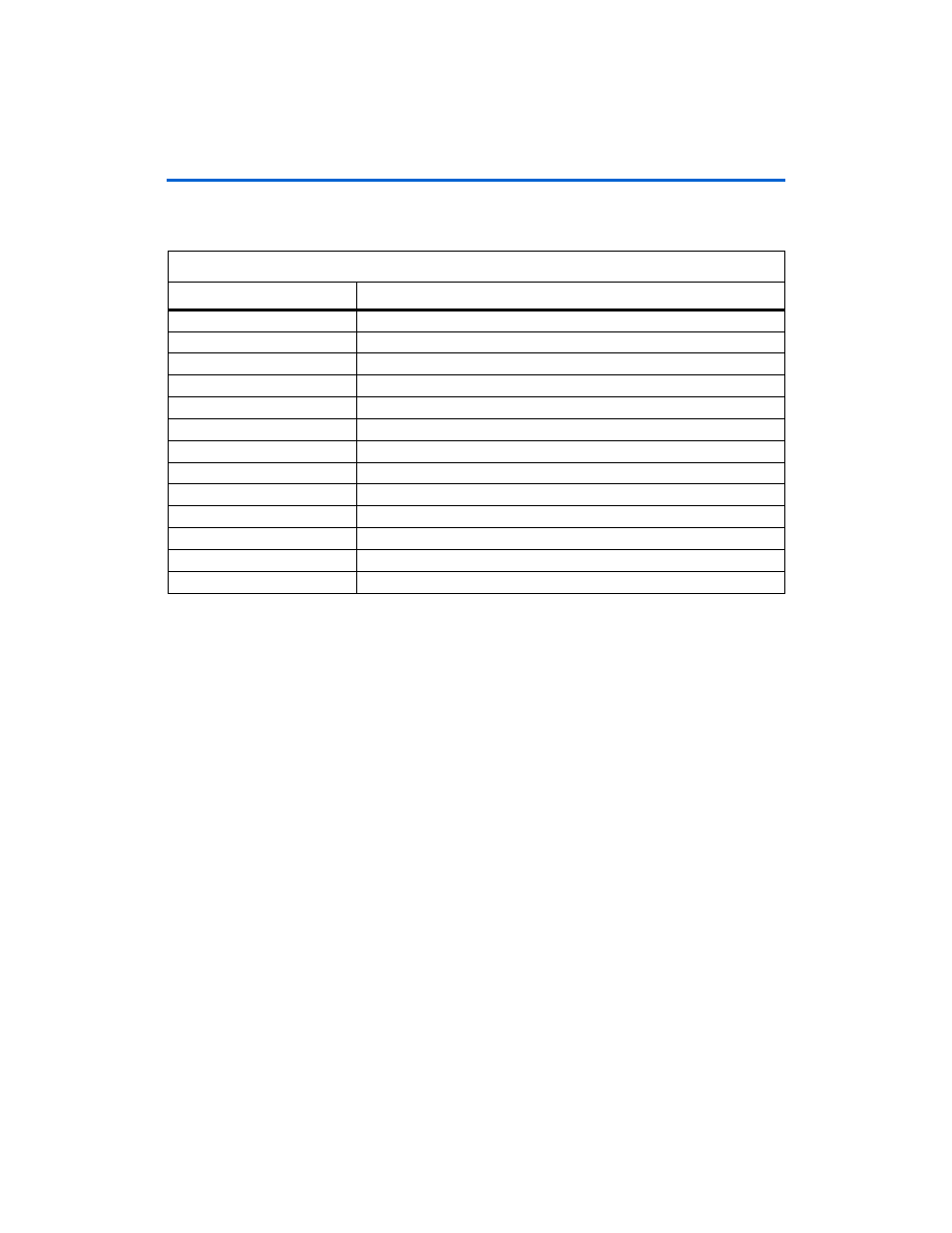

Table 7–17. PCI-Avalon Bridge Register Map

Address Range

Register

0x0040

PCI interrupt status register

0x0050

PCI interrupt enable register

0x0800-0x081F

PCI-to-Avalon mailbox registers – read/write

0x0900-0x091F

Avalon-to-PCI mailbox registers – read only

0x1000-0x1FFF

Avalon-to-PCI address translation table

0x2C00

General configuration parameters – read only

0x2C04

Performance parameters – read only

0x2C08

Avalon-to-PCI address translation parameters – read only

0x3060

Avalon interrupt status register

0x306C

Current PCI status register – read only

0x3070

Avalon interrupt enable register

0x3A00–0x3A1F

Avalon-to-PCI mailbox registers – read/write

0x3B00–0x3B1F

PCI-to-Avalon mailbox registers – read only