Latency timer register, Header type register – Altera PCI Compiler User Manual

Page 110

3–36

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Configuration Registers

Latency Timer Register

The latency timer register is an 8-bit register with bits 2, 1, and 0 tied to

ground. The register defines the maximum amount of time, in PCI bus

clock cycles, that the PCI function can retain ownership of the PCI bus.

After initiating a transaction, the function decrements its latency timer by

one on the rising edge of each clock cycle. The default value of the latency

timer register is 0x00. Refer to

1

This register is implemented in the pci_mt64 and pci_mt32

functions only.

Header Type Register

Header type is an 8-bit read-only register that identifies the PCI function

as a single-function device. The default value of the header type register

is 0x00. Refer to

.

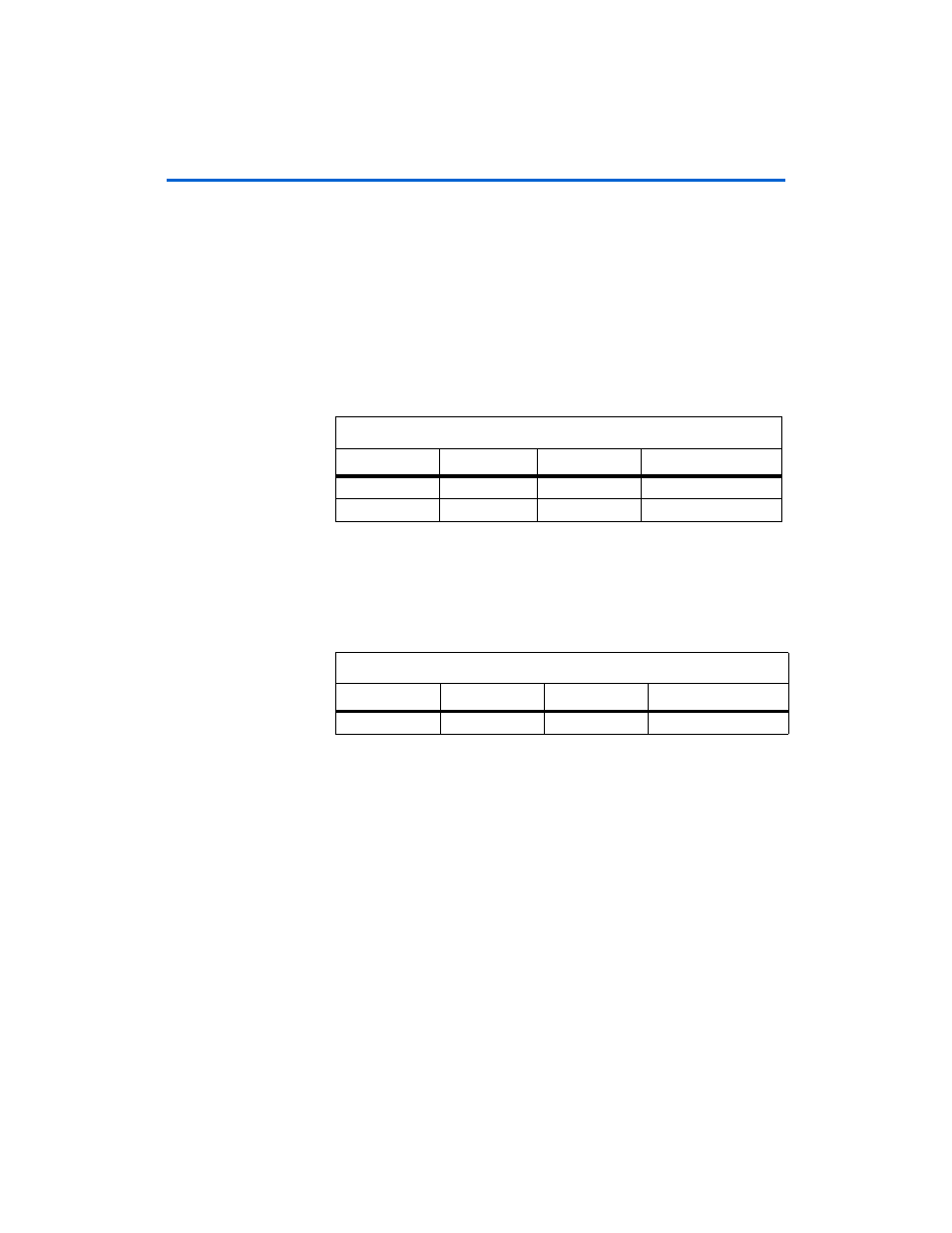

Table 3–21. Latency Timer Register Format

Data Bit

Mnemonic

Read/Write

Definition

2..0

lat_tmr

Read

Latency timer register

7..3

lat_tmr

Read/write

Latency timer register

Table 3–22. Header Type Register Format

Data Bit

Mnemonic

Read/Write

Definition

7..0

header

Read

PCI header type