Altera PCI Compiler User Manual

Page 292

7–24

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

PCI Target Operation

The read requests are passed through the PCI-to-Avalon

command/write data buffer, so that they maintain their ordering with

respect to the previous write requests.

Memory read requests that match a prefetchable BAR are forwarded to

the interconnect as burst read requests. The size of the burst depends on

the PCI command used:

■

The cacheline wrap mode reads are treated as Single-Cycle Transfers

Only and are always set to a burst length of one. Therefore, one

DWORD

is transferred in 32-bit mode, and two DWORDs are transferred

64-bit mode.

■

The PCI memory read and memory read line commands set the burst

count to transfer data up to the next 32-byte address boundary.

Therefore, the burst count is set from 1-8 in 32-bit mode and 1-4 in

64-bit mode. For example, if the least significant byte of the PCI

address is 0x08, the burst count used for 32-bit mode will be 6 and

64-bit mode will be 3.

■

The PCI memory read multiple command sets the burst count to

transfer data up to the second 32-byte boundary. Thus, the burst

count is set from 9-16 in 32-bit mode and 5-8 in 64-bit mode. So, the

maximum number of bytes transferred in the PCI memory read

multiple command is 64-bytes where the end address must be

32-byte aligned. For example, if the least significant byte of the PCI

address is 0x08, the burst count used for 32-bit is 14 and burst count

used for 64-bit is 7. Refer to

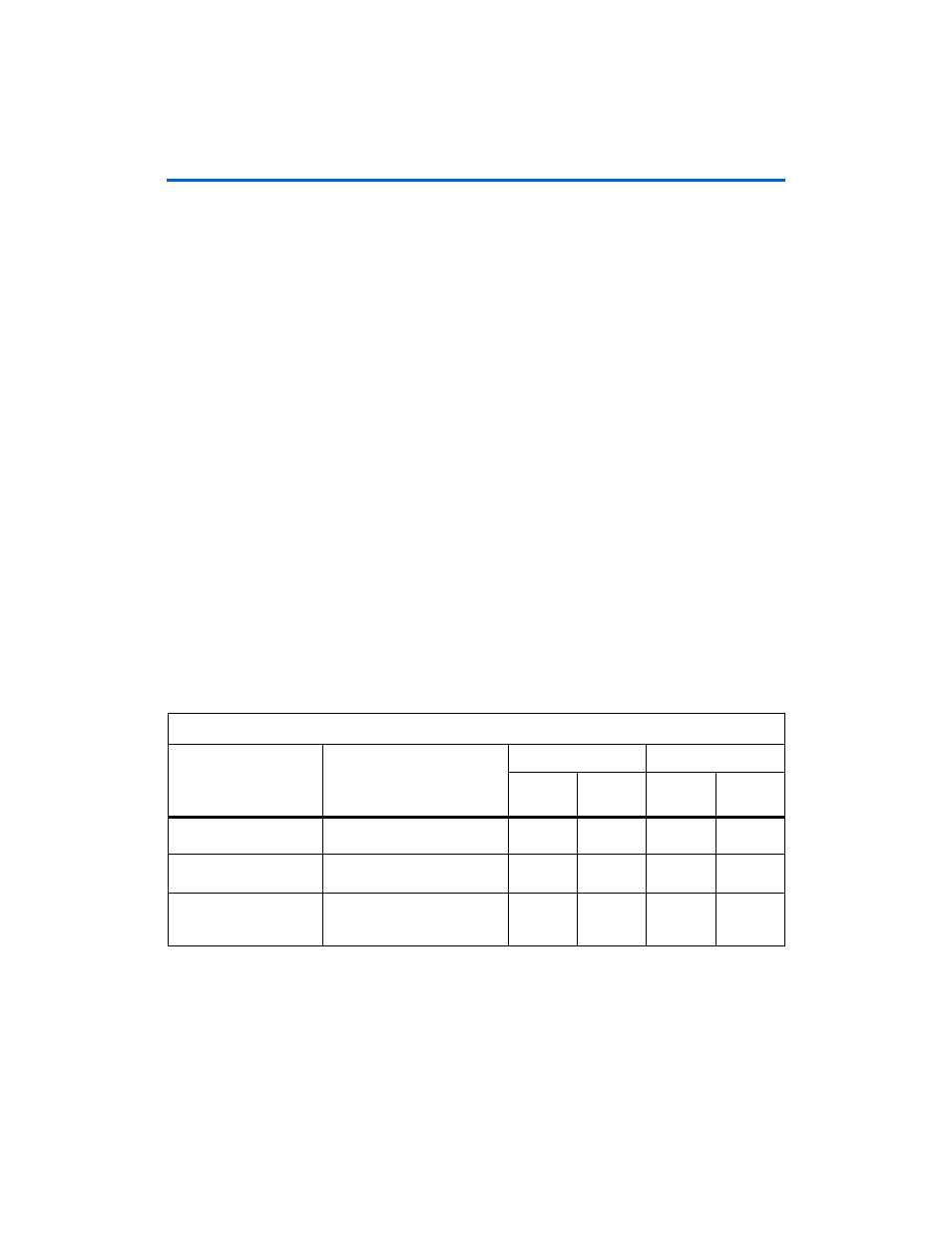

Table 7–7. Burst Size for PCI Target Prefetchable Read Requests

PCI Command

Transfers

32-Bit

64-Bit

Burst

Count

Transfer

Size

Burst

Count

Transfer

Size

Any read that specifies

cacheline wrap mode

1 1

1

DWORD

1

2

DWORD

s

Memory read and memory

read line

As many to reach address that is

aligned to 32-bytes.

1-8

1-8

DWORD

s

1-4

2-8

DWORD

s

Memory read multiple

Transfers up to 64-bytes so that

the address reaches the second

32-byte boundary.

9-16

9-16

DWORD

s

5-8

10-16

DWORD

s