Read-only configuration registers, Table 7–22 – Altera PCI Compiler User Manual

Page 322

7–54

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Control & Status Registers

The lower order address bits that are treated as a pass through between

Avalon-MM and PCI, and the number of pass-through bits, are defined

by the size of page in the address translation table and are always forced

to 0 in the hardware table. For example, if the page size is 4 KBytes, the

number of pass-through bits is log

2

(page size) = log

2

(4 KBytes) = 12.

Read-Only Configuration Registers

These registers reflect some of the configuration parameters that enable

the software to understand the configuration of the PCI-Avalon bridge.

Providing this information in these registers allows the software to adapt

to the bridge configuration at run time without specifying the same

parameter settings to the software at compilation time.

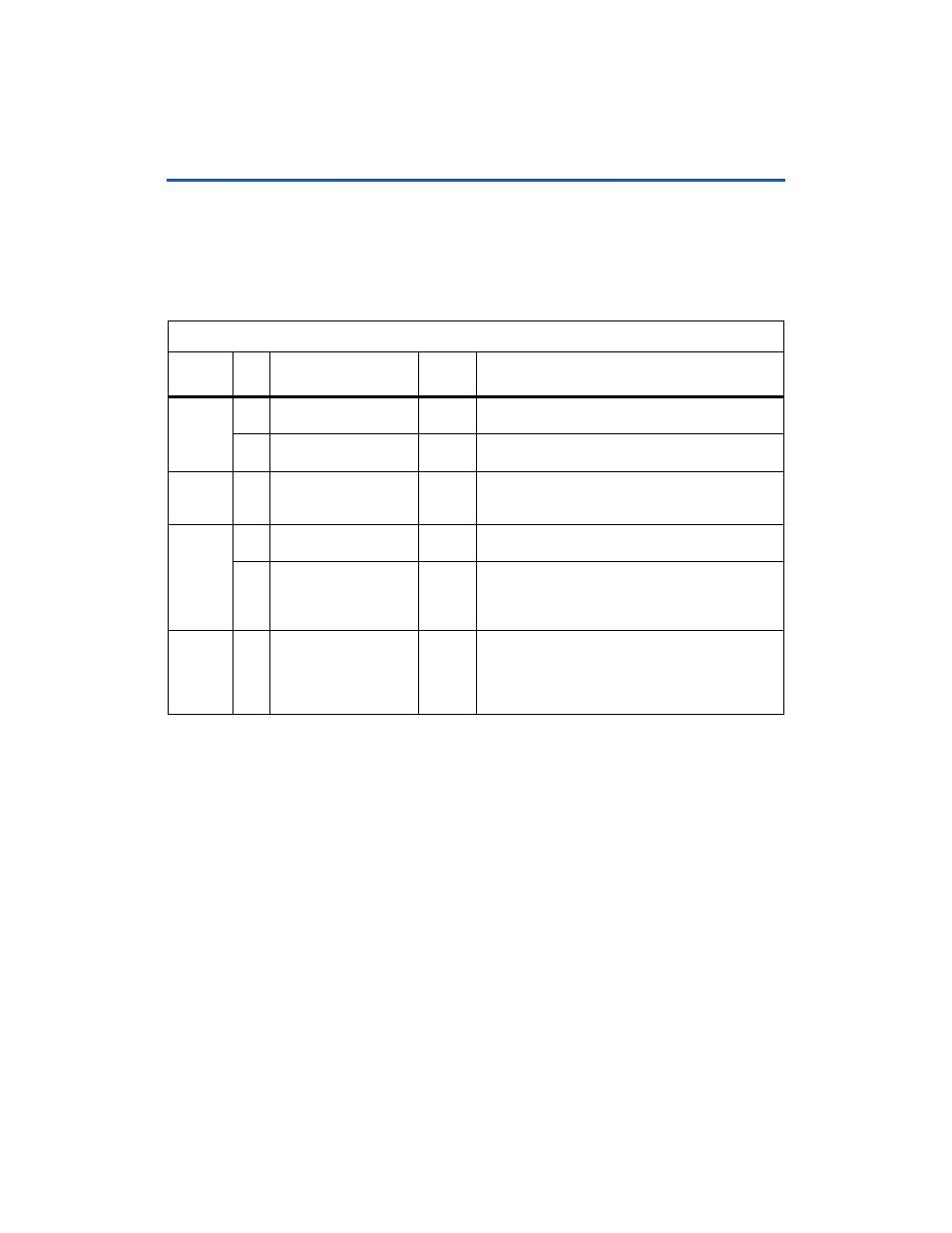

Table 7–22. Avalon-to-PCI Address Translation Table – Address Range: 0x1000-0x1FFF

Address

Bit

Name

Access

Mode

Description

0x1000

1:0

A2P_ADDR_SPACE0

RW

Address space indication for entry 0. Refer to

for the definition of these bits.

31:2

A2P_ADDR_MAP_LO0

RW

Lower bits of Avalon-to-PCI address map entry 0. The

pass through bits are not writable and are forced to 0.

0x1004

31:0

A2P_ADDR_MAP_HI0

RW

Upper bits of Avalon-to-PCI address map entry 0.

When the PCI bus width is 32 bits, these bits are not

writable and are forced to 0.

0x1008

1:0

A2P_ADDR_SPACE1

RW

Address Space indication for entry 1. Refer to

for the definition of these bits.

31:2

A2P_ADDR_MAP_LO1

RW

Lower bits of Avalon-to-PCI address map entry 1. Pass

through bits are not writable and are forced to 0.

This entry is only implemented if the number of pages

in the address translation table is greater than 1.

0x100C

31:0

A2P_ADDR_MAP_HI1

RW

Upper bits of Avalon-to-PCI address map entry 1.

When the PCI bus width is 32 bits, these bits are not

writable and are forced to 0.

This entry is only implemented if the number of pages

in the address translation table is greater than 1.

Note to

:

(1)

The above table entries are repeated for the number of pages you selected in the Avalon configuration tab

.

I

f the Number of Address Pages field is set to the maximum of 512, then 0x1FF8 will contain

A2P_ADDR_MAP_LO511 and 0x1FFC will contain A2P_ADDR_MAP_HI511. Refer to