Testbench specifications, Testbench specifications –4, File – Altera PCI Compiler User Manual

Page 334

8–4

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Testbench Specifications

Refer to

“Simulation Flow” on page 8–15

for more information on the

modified testbench files.

Testbench

Specifications

This section describes the modules used by the PCI testbench including

master commands, setting and controlling target termination responses,

bus parking, and PCI bus speed settings. Refer to

for a block

diagram of the PCI testbench. The Altera PCI testbench has the following

modules:

■

Master transactor (mstr_tranx)

■

Target transactor (trgt_tranx)

■

Bus monitor (monitor)

■

Clock generator (clk_gen)

■

Arbiter (arbiter)

■

Pull ups (pull_ups)

■

A local reference design

The PCI testbench consists of VHDL and Verilog HDL. If your application

requires a feature that is not supported by the PCI testbench, you can

modify the source code to add the feature. You can also modify the

existing behavior to fit your application needs.

shows the PCI bus transactions supported by the PCI testbench.

pci_tb

This top-level file instantiates all the testbench

modules.

Note to

:

(1)

All files are provided in both VHDL and Verilog HDL.

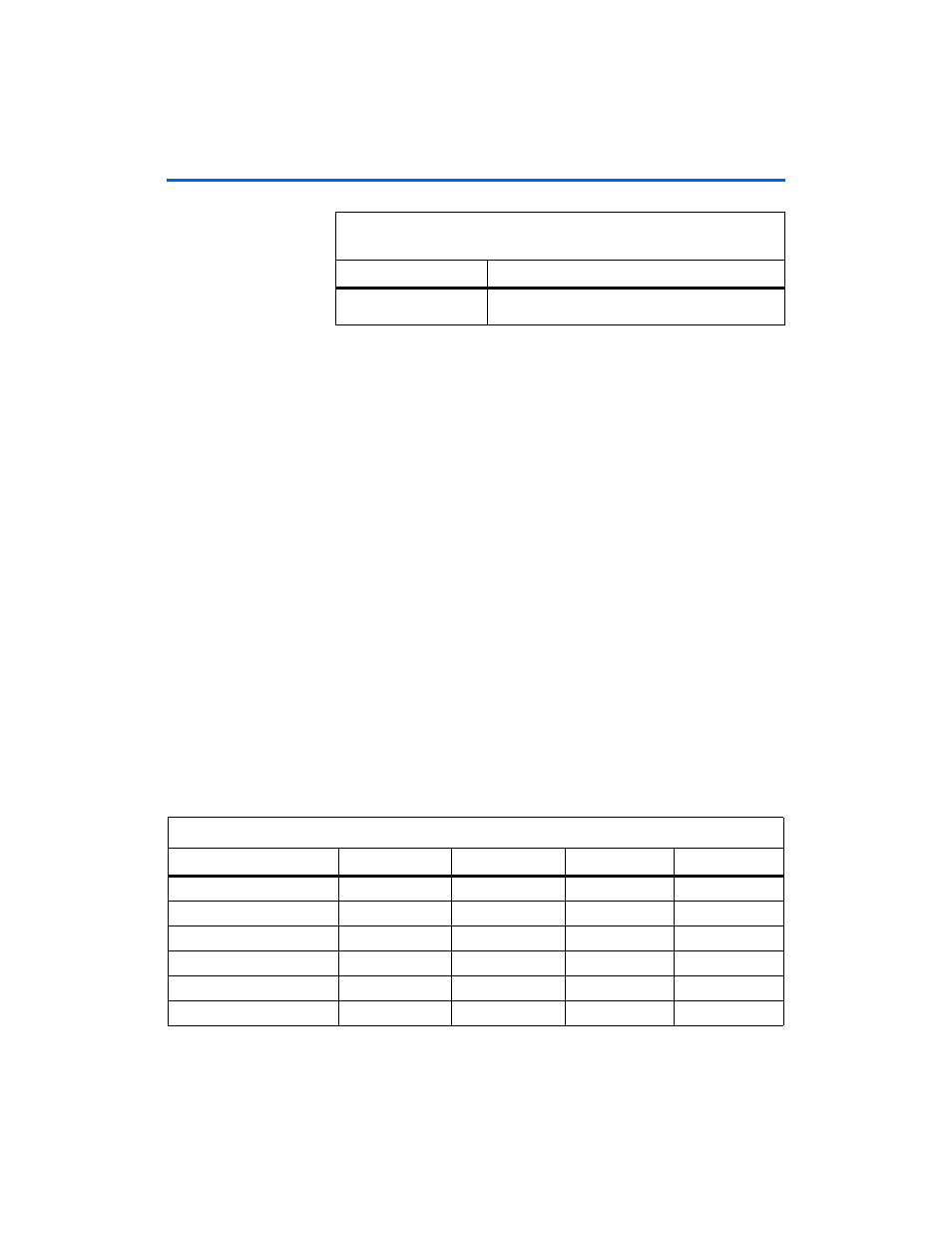

Table 8–1. Files Contained in the pci_sim/

Directory (Part 2 of 2)

File

(1)

Description

Table 8–2. PCI Testbench PCI Bus Transaction Support (Part 1 of 2)

Transactions

Master Transactor Target Transactor

Local Master

Local Target

Interrupt acknowledge cycle

I/O read

v

v

v

v

I/O write

v

v

v

v

Memory read

v

v

v

v

Memory write

v

v

v

v

Configuration read

v

v