Master transactor (mstr_tranx), Procedures and tasks sections – Altera PCI Compiler User Manual

Page 335

Altera Corporation

User Guide Version 11.1

8–5

October 2011

PCI Compiler

Testbench

shows the testbench's target termination support. The master

transactor and the local master respond to the target terminations by

terminating the transaction gracefully and releasing the PCI bus.

Master Transactor (mstr_tranx)

The master transactor simulates the master behavior on the PCI bus. It

serves as an initiator of PCI transactions for Altera PCI testbench. The

master transactor has three main sections:

■

PROCEDURES (VHDL) or TASKS (Verilog HDL)

■

INITIALIZATION

■

USER COMMANDS

PROCEDURES and TASKS Sections

The PROCEDURES (VHDL) and TASKS (Verilog HDL) sections define

the events that are executed for the user commands supported by the

master transactor. The events written in the PROCEDURES and TASKS

sections follow the phases of a standard PCI transaction as defined by the

PCI Local Bus Specification, Revision 3.0, including:

■

Address phase

■

Turn-around phase (read transactions)

■

Data phases

■

Turn-around phase

Configuration write

v

v

Memory read multiple

v

Dual address cycle

Memory read line

v

Memory write and invalidate

v

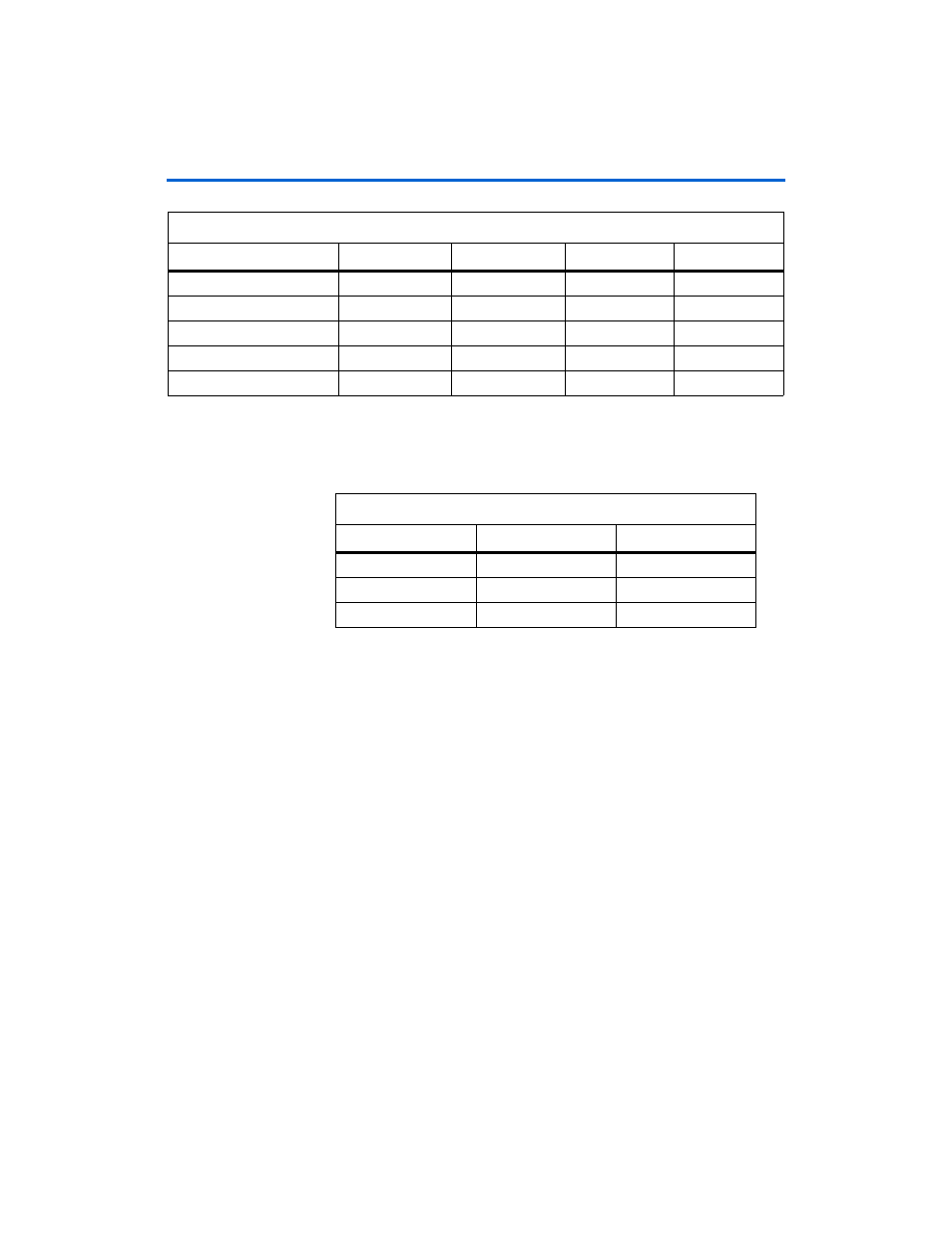

Table 8–2. PCI Testbench PCI Bus Transaction Support (Part 2 of 2)

Transactions

Master Transactor Target Transactor

Local Master

Local Target

Table 8–3. PCI Testbench Target Termination Support

Features

Master Transactor

Target Transactor

Target abort

v

Target retry

v

v

Target disconnect

v

v