Avalon-to-pci address translation table – Altera PCI Compiler User Manual

Page 321

Altera Corporation

User Guide Version 11.1

7–53

October 2011

Functional Description

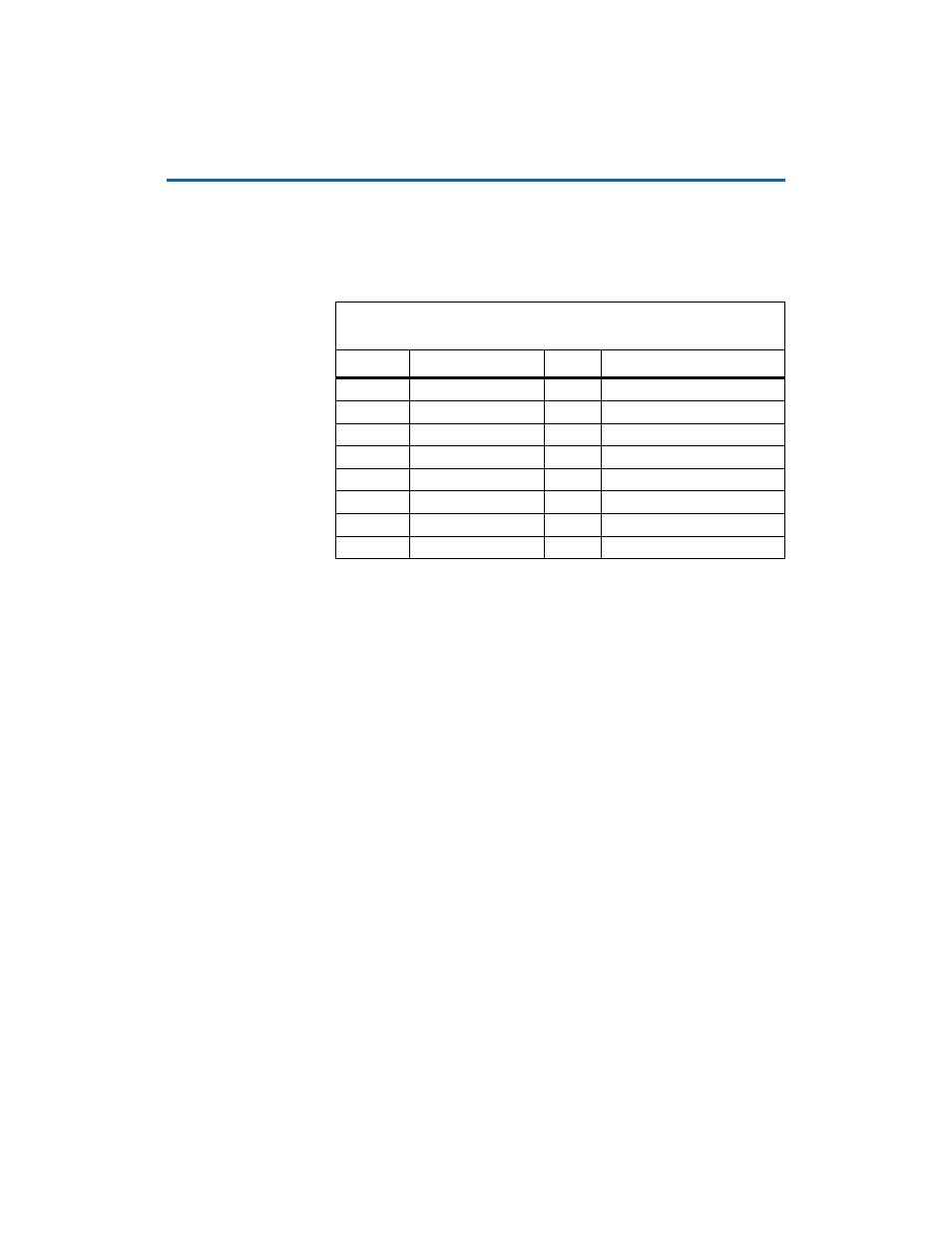

The Avalon-to-PCI mailbox registers are readable at the addresses shown

in

. PCI Hosts use these addresses to read the mailbox

information after being signaled by the corresponding bits in the PCI

interrupt status register.

Avalon-to-PCI Address Translation Table

Unless fixed mapping is used, the Avalon-to-PCI address translation

table is writable via the Control Register Access Avalon Slave

port. In effect, the translation table is writable if the Dynamic Translation

Table is selected (refer to

“Avalon Configuration” on page 6–16

). The

translation table is always readable at the same addresses. (

Each entry in the PCI address translation table is always 64 bits (8 bytes)

wide, regardless of whether the system supports 64-bit PCI addressing.

64-bit addressing is supported only when the PCI bus width is 64 bits.

This ensures that the table address always has the same register

addressing regardless of PCI addressing width.

Table 7–21. Avalon-to-PCI Mailbox Registers – Address Range:

0x0900-0x091F

Address

Name

Access

Description

0x0900

A2P_MAILBOX0

RO

Avalon-to-PCI mailbox 0.

0x0904

A2P_MAILBOX1

RO

Avalon-to-PCI mailbox 1.

0x0908

A2P_MAILBOX2

RO

Avalon-to-PCI mailbox 2.

0x090C

A2P_MAILBOX3

RO

Avalon-to-PCI mailbox 3.

0x0910

A2P_MAILBOX4

RO

Avalon-to-PCI mailbox 4.

0x0914

A2P_MAILBOX5

RO

Avalon-to-PCI mailbox 5.

0x0918

A2P_MAILBOX6

RO

Avalon-to-PCI mailbox 6.

0x091C

A2P_MAILBOX7

RO

Avalon-to-PCI mailbox 7.