Cfg_wr, Mem_wr_32 – Altera PCI Compiler User Manual

Page 338

8–8

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Testbench Specifications

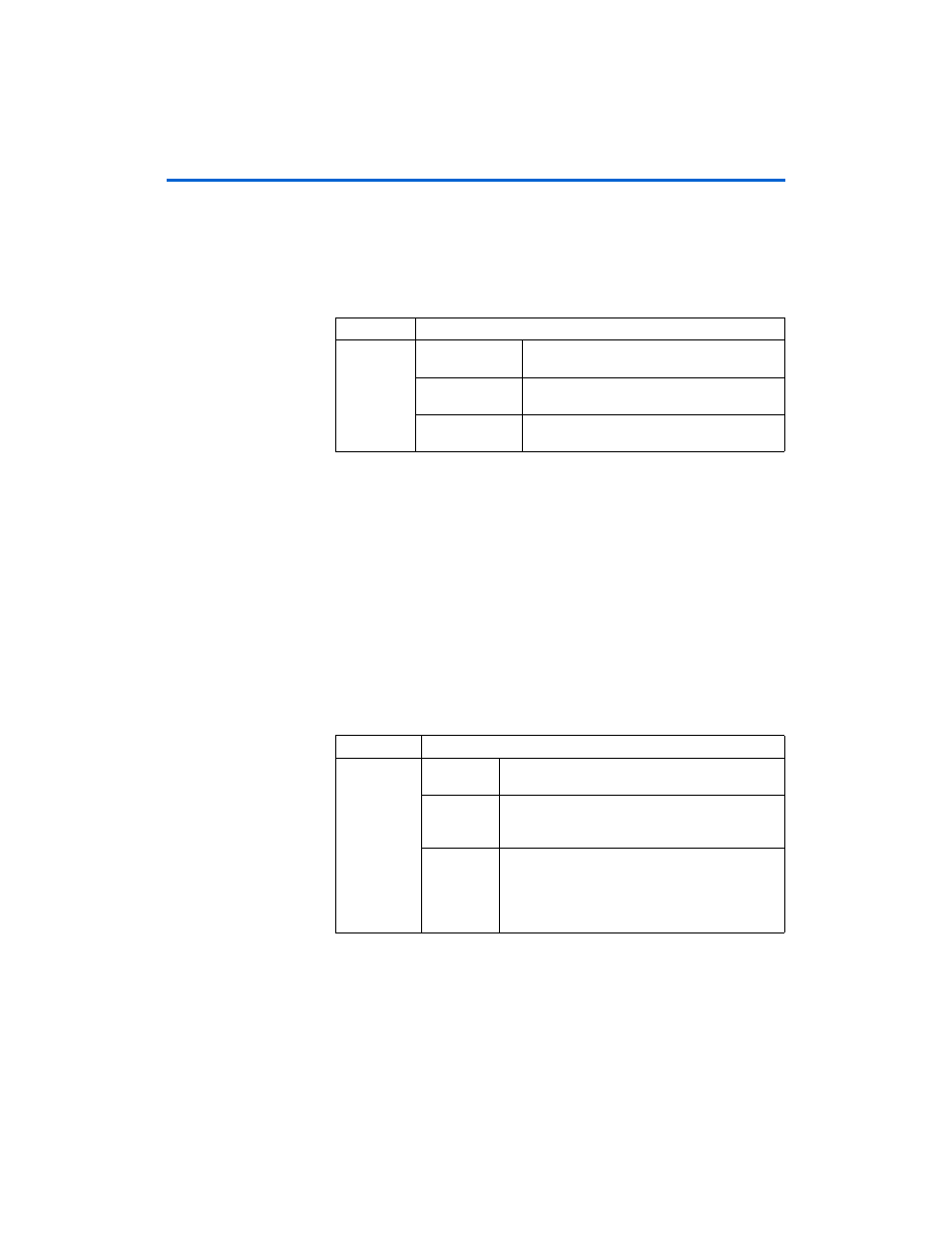

cfg_wr

The cfg_wr command performs single-cycle PCI configuration write

transactions with the address, data, and byte enable provided in the

command arguments.

mem_wr_32

The mem_wr_32 command performs a memory write with the address

and data provided in the command arguments. This command can

perform a single-cycle or burst 32-bit memory write depending on the

number of DWORDs provided in the command argument.

■

The mem_wr_32 command performs a single-cycle 32-bit memory

write if the DWORD value is 1.

■

The mem_wr_32 command performs a burst-cycle 32-bit memory

write if the DWORD value is greater than 1. In a burst transaction, the

first data phase uses the data value provided in the command. The

subsequent data phases use values incremented sequentially by 1

from the data provided in the command argument.

Syntax:

cfg_wr(address, data, byte_enable)

Arguments:

address

Transaction address. This value must be in

hexadecimal radix.

data

Transaction data. The data must be in

hexadecimal radix.

byte_enable

Transaction byte enable. The byte enable

value must be in hexadecimal radix

Syntax:

mem_wr_32(address, data, dword)

Arguments:

address

Transaction address. This value must be in

hexadecimal radix.

data

Data used for the first data phase. Subsequent

data phases use a value incremented sequentially

by 1. This value must be in hexadecimal radix.

dword

The number of

DWORD

s written during the

transaction. A value of 1 indicates a single-cycle

memory write transaction. A value greater than one

indicates a burst transaction. This value must be an

integer.