Pci mailbox register access – Altera PCI Compiler User Manual

Page 320

7–52

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Control & Status Registers

Avalon-MM interrupts can also be enabled for all of the conditions in bits

31:0. However, only one of the Avalon-MM or PCI interrupts (not both)

should be enabled for any given bit. There is typically a single process in

either the PCI or Avalon-MM domain that is responsible for handling the

condition reported by the interrupt.

PCI Mailbox Register Access

The PCI bus typically needs write access to a set of PCI-to-Avalon mailbox

registers and read-only access to a set of Avalon-to-PCI mailbox registers.

lists the specific number (1 or 8) of available

mailbox registers.

The PCI-to-Avalon mailbox registers are writable at the addresses shown

in

. Writing to one of these registers causes the corresponding

bit in the Avalon-MM interrupt status register to be set to 1.

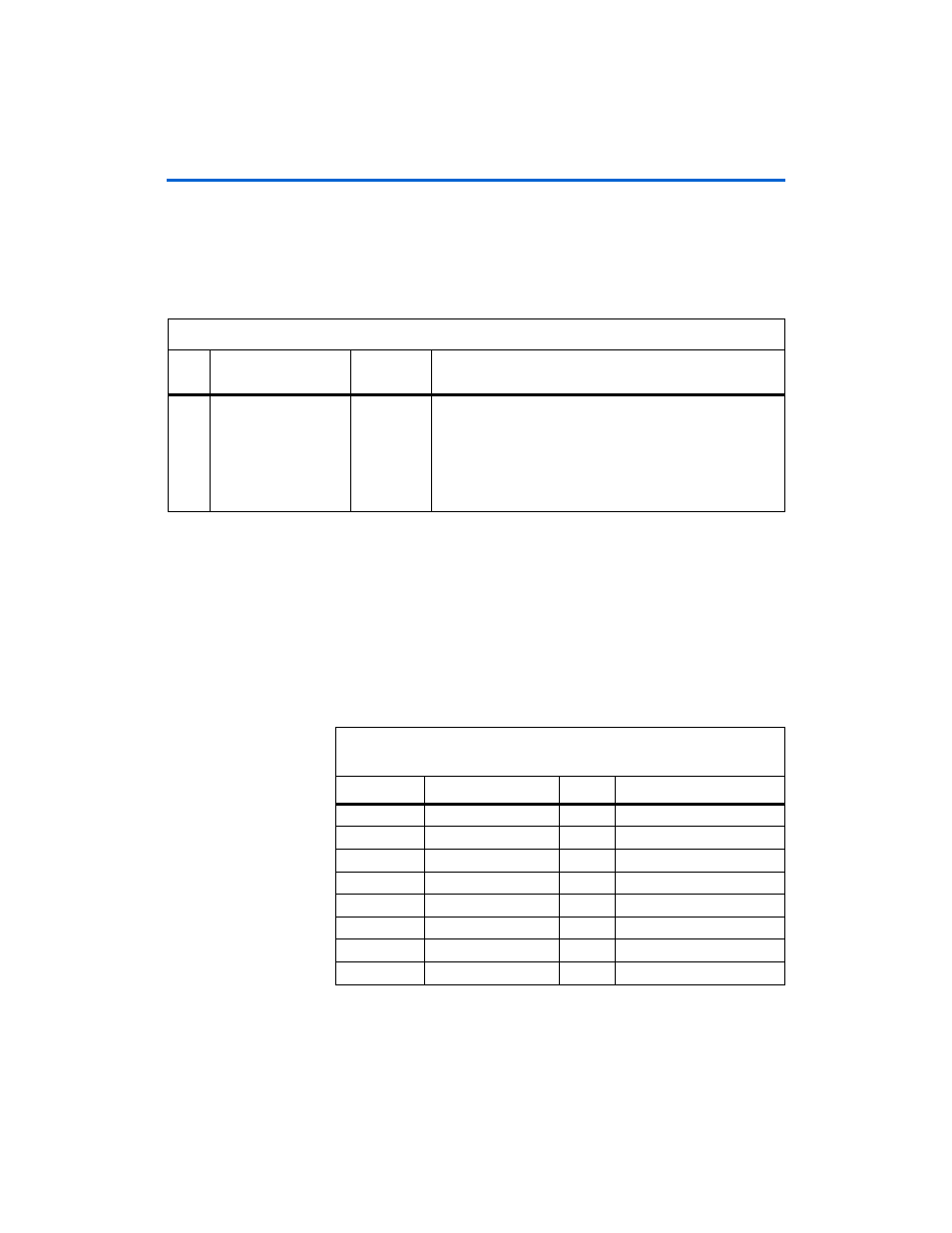

Table 7–19. PCI Interrupt Enable Register – Address: 0x0050

Bit

Name

Access

Mode

Description

31:0

One-to-one enable

mapping to the PCI

interrupt status register

bits

RW

When set to 1, indicates that the associated bit in the PCI

interrupt status register will cause the PCI interrupt line

(

intan

) to be asserted if not disabled by the PCI command

register.

Only bits implemented in the PCI interrupt status register are

implemented in the enable register. Unimplemented bits cannot

be set to 1.

Table 7–20. PCI-to-Avalon Mailbox Registers – Address Range:

0x0800-0x081F

Address

Name

Access

Description

0x0800

P2A_MAILBOX0

RW

PCI-to-Avalon mailbox 0.

0x0804

P2A_MAILBOX1

RW

PCI-to-Avalon mailbox 1.

0x0808

P2A_MAILBOX2

RW

PCI-to-Avalon mailbox 2.

0x080C

P2A_MAILBOX3

RW

PCI-to-Avalon mailbox 3.

0x0810

P2A_MAILBOX4

RW

PCI-to-Avalon mailbox 4.

0x0814

P2A_MAILBOX5

RW

PCI-to-Avalon mailbox 5.

0x0818

P2A_MAILBOX6

RW

PCI-to-Avalon mailbox 6.

0x081C

P2A_MAILBOX7

RW

PCI-to-Avalon mailbox 7.