Altera PCI Compiler User Manual

Page 27

Altera Corporation

User Guide Version 11.1

15

October 2011

About PCI Compiler

lists memory utilization and performance data for Cyclone II

devices.

lists memory utilization and performance data for Stratix,

Stratix GX, and Cyclone devices.

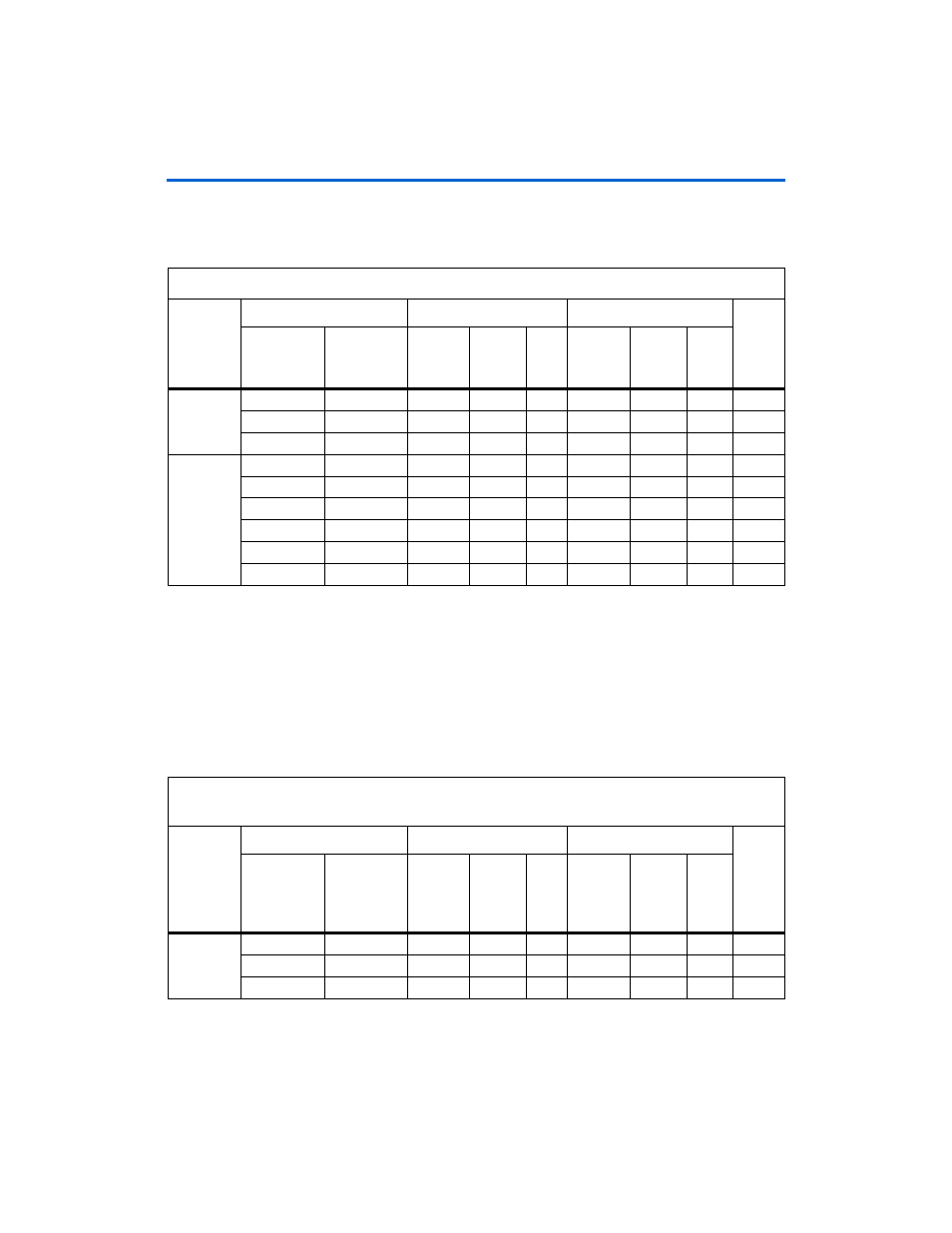

Table 9. Memory Utilization & Performance Data for Cyclone II Devices

PCI

Device

Mode

Performance Setting as:

32-Bit PCI Interface

64-Bit PCI Interface

PCI

f

MAX

(MHz)

PCI Target

PCI Master

Logic

Elements

(LEs)

M4K

Memory

Blocks

I/O

Pins

Logic

Elements

(LEs)

M4K

Memory

Blocks

I/O

Pins

PCI

Target-

Only

Min

N/A

547

0

48

1,114

0

87

>67

Typical

N/A

1,113

4

48

1,565

6

87

>67

Max

N/A

1,605

4

48

2,051

6

87

>67

PCI

Master/

Target

Min

Typical

2,117

7

50

3,075

9

89

>67

Typical

Typical

2,319

9

50

3,391

13

89

>67

Max

Typical

2,806

9

50

3,915

13

89

>67

Min

Max

3,096

7

50

4,655

9

89

>67

Typical

Max

3,328

9

50

4,939

13

89

>67

Max

Max

3,806

9

50

5,454

13

89

>67

Notes to

(1)

Min

= Single-cycle transactions

Typical

= Burst transactions with a single pending read

Max

= Burst transactions with multiple pending reads

(2)

The data was obtained by performing compilations on a Cyclone II EP2C35F672C7 device. Each of the device types

was parameterized to use one BAR that reserved 1 MByte of memory on the Avalon-MM side. For the PCI

Master/Target Peripheral mode, one MByte of memory was reserved on the PCI side.

Table 10. Memory Utilization & Performance Data for Stratix, Stratix GX & Cyclone Devices

(Part

1

of 2)

PCI

Device

Mode

Performance Setting as:

32-Bit PCI Interface

64-Bit PCI Interface

PCI

f

MAX

(MHz)

PCI Target

PCI Master

Logic

Elements

(LEs)

M512

Memory

Blocks

I/O

Pins

Logic

Elements

(LEs)

M512

Memory

Blocks

I/O

Pins

PCI

Target-

Only

Min

N/A

852

0

48

1,186

0

87

>67

Typical

N/A

1,460

4

48

1,949

6

87

>67

Max

N/A

1,940

4

48

2,442

6

87

>67