Altera PCI Compiler User Manual

Page 100

3–26

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

PCI Bus Signals

shows definitions for the local master transaction status

register outputs.

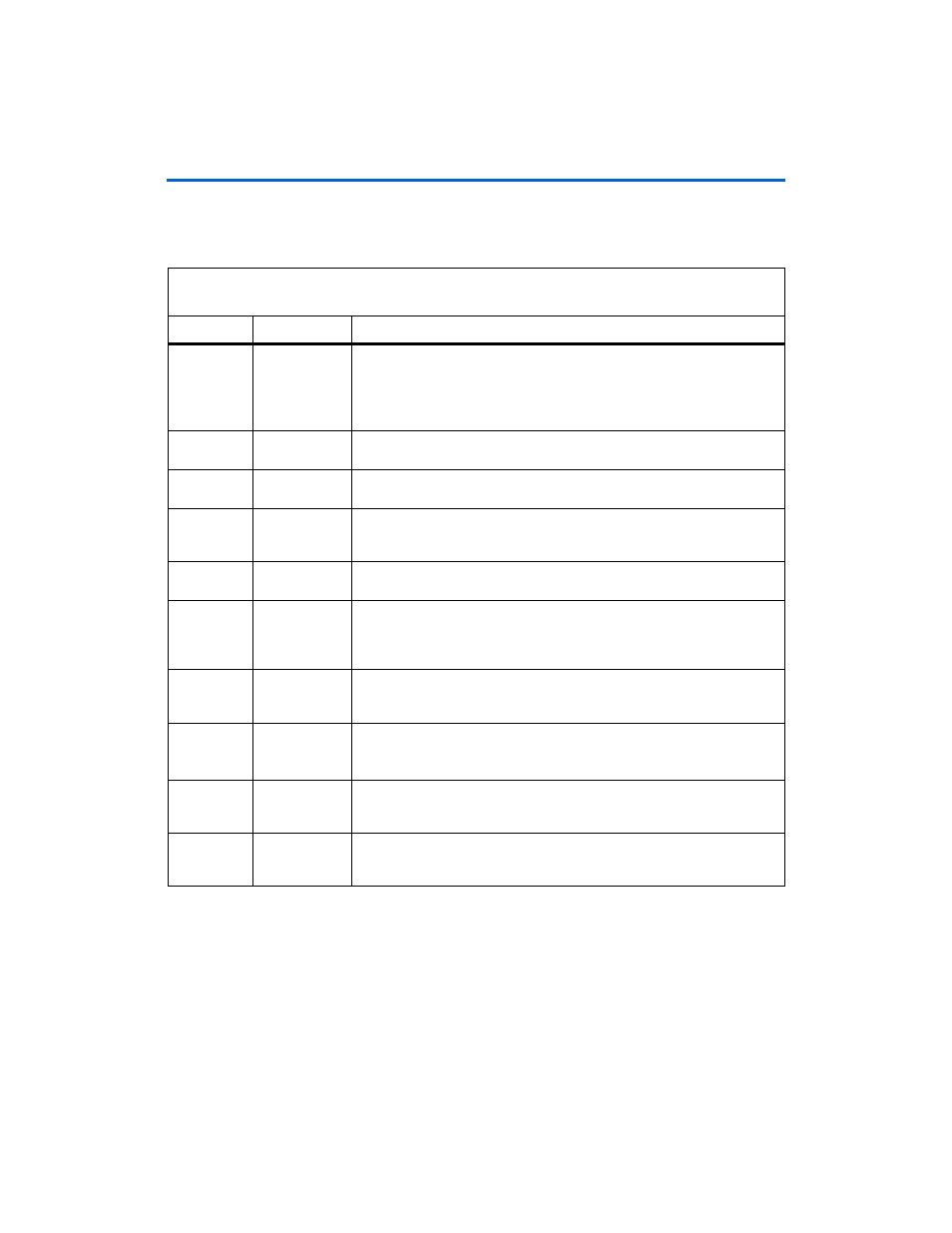

Table 3–10. pci_mt64 & pci_mt32 Local Master Transaction Status Register (lm_tsr[9..0]) Bit

Definition

Bit Number

Bit Name

Description

0

request

Request. This signal indicates that the

pci_mt64

or

pci_mt32

function is

requesting mastership of the PCI bus (i.e., it is asserting its

reqn

signal). The

request

bit is not asserted if the following is true: The PCI bus arbiter has

parked on the

pci_mt64

or

pci_mt32

function and the

gntn

signal is

already asserted when the function requests mastership of the bus.

grant

Grant. This signal is active after the

pci_mt64

or

pci_mt32

function has

detected that

gntn

is asserted.

adr_phase

Address phase. This signal is active during a PCI address phase where

pci_mt64

or

pci_mt32

is the bus master.

3

dat_phase

Data phase. This signal is active while the

pci_mt64

or

pci_mt32

function

is in data transfer mode. The signal is active after the address phase and

remains active until the turn-around state begins.

4

lat_exp

Latency timer expired. This signal indicates that

pci_mt64

or

pci_mt32

terminated the master transaction because the latency timer counter expired.

5

retry

Retry detected. This signal indicates that the

pci_mt64

or

pci_mt32

function terminated the master transaction because the target issued a retry.

Per the PCI specification, a transaction that ends in a retry must be retried at

a later time.

6

disc_wod

Disconnect without data detected. This signal indicates that the

pci_mt64

or

pci_mt32

signal terminated the master transaction because the target

issued a disconnect without data.

7

disc_wd

Disconnect with data detected. This signal indicates that

pci_mt64

or

pci_mt32

terminated the master transaction because the target issued a

disconnect with data.

8

dat_xfr

Data transfer. This signal indicates that a successful data transfer occurred on

the PCI side in the preceding clock cycle. This signal can be used by the local

side to keep track of how much data was actually transferred on the PCI side.

9

trans64

64-bit transaction. This signal indicates that the target claiming the transaction

asserted its

ack64n

signal. Because

pci_mt32

does not request 64-bit

transactions, this signal is reserved.

Note to

:

(1)

Some arbiters may initially assert gntn (in response to either the pci_mt64 or pci_mt32 function requesting

mastership of the PCI bus), but then deassert gntn (before the pci_mt64 or pci_mt32 have asserted framen) to

give mastership of the bus to a higher priority device. In systems where this situation may occur, the local side logic

should hold the address and command on the l_adi[63..0] and

l_cbeni[7..0]

buses until the adr_phase

bit is asserted (lm_tsr[2]) to ensure that the pci_mt64 or pci_mt32 function has assumed mastership of the

bus and that the current address and command bits have been transferred.