Avalon-mm interrupt status register – Altera PCI Compiler User Manual

Page 324

7–56

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Control & Status Registers

lists some key performance sizing information of the core.

lists the configuration of the Avalon-to-PCI address

translation table.

Avalon-MM Interrupt Status Register

The Avalon-MM interrupt status register contains the status of various

signals in the PCI-Avalon bridge logic, and it allows Avalon-MM

interrupts to be signaled when enabled via the Avalon-MM interrupt

enable register. These registers are not intended to be accessed by the

PCI-Avalon bridge master ports. However, there is nothing in the

hardware that prevents this.

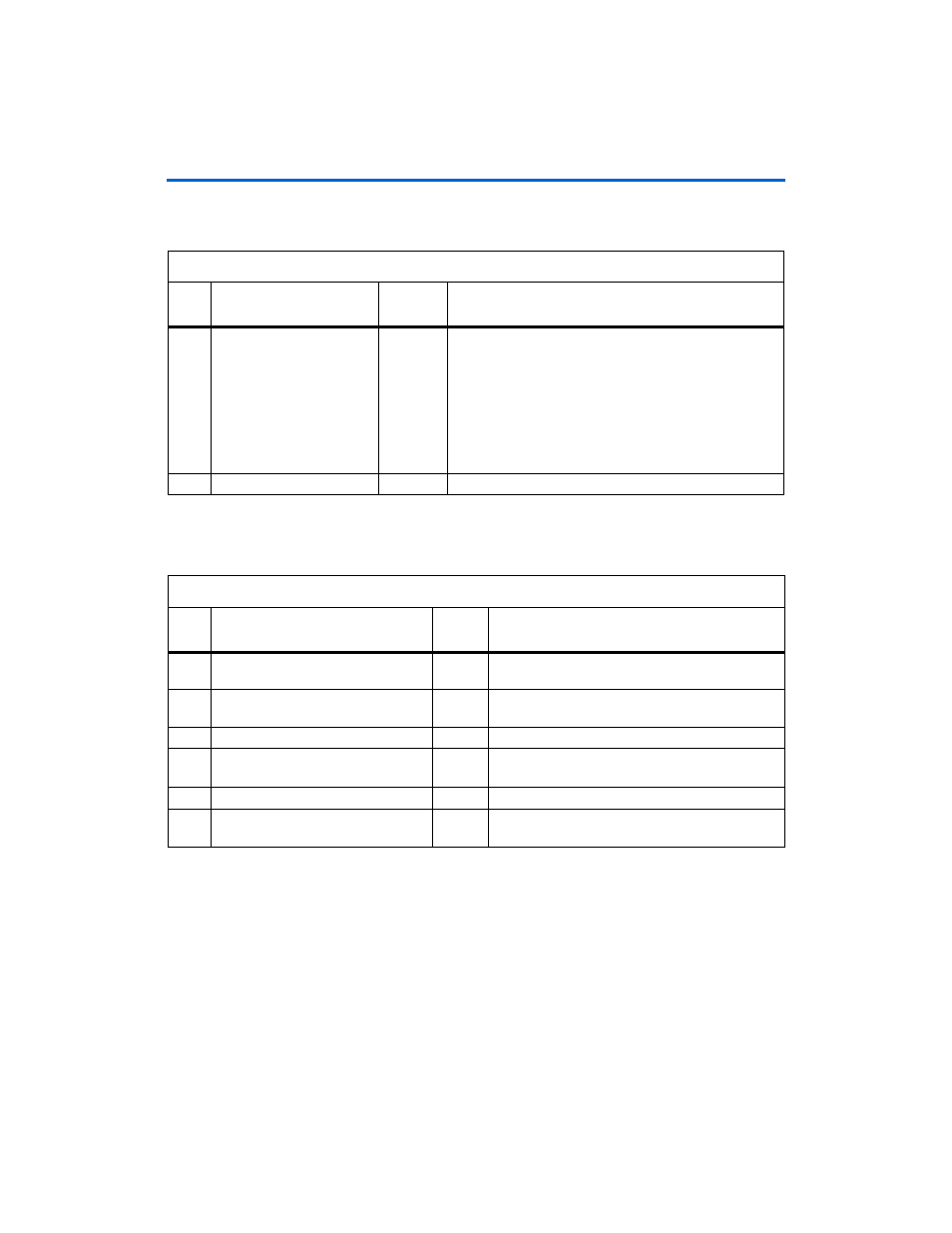

Table 7–24. Performance Parameters – Address 0x2C04

Bit

Name

Access

Mode

Description

15:0

A2P_WRITE_CD_DEPTH

RO

Reflects the depth of the Avalon-to-PCI command and data

buffer. The software may not want to issue burst writes (via

Avalon DMA or similar) to the bridge that exceed half this

value in length. While larger bursts are supported, if the PCI

bus is slow or very busy, larger bursts may take a very long

time to complete on Avalon, preventing smaller requests

from other Avalon-MM masters from being recognized.

Backing up those other requests could slow overall

performance.

31:16

Reserved

RO

Reserved

Table 7–25. Avalon-to-PCI Address Translation Parameters – Address 0x2C08

Bit

Name

Access

Mode

Description

0

A2P_ADDR_MAP_IS_FIXED

RO

Indicates that the Fixed Translation Table (refer to

“Avalon Configuration” on page 6–16

) is selected.

1

A2P_ADDR_MAP_IS_READABLE

RO

Indicates if the Avalon-to-PCI translation table is

readable. This bit is always set to 1.

7:2

Reserved

RO

Reserved

13:8

A2P_ADDR_MAP_PASS_THRU_BIT

S

RO

Indicates the number of pass-through bits (binary

encoded).

15:14

Reserved

RO

Reserved

31:16

A2P_ADDR_MAP_NUM_ENTRIES

RO

Indicates the number of pages in the Address

Translation Table Size field.