Revision id register – Altera PCI Compiler User Manual

Page 108

3–34

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Configuration Registers

Revision ID Register

Revision ID is an 8-bit read-only register that identifies the revision

number of the device. The value of this register is assigned by the

manufacturer (e.g., Altera for the PCI MegaCore functions.) For the

Altera PCI MegaCore functions, the default value of the revision ID

register is the revision number of the function. Refer to

. You

can change the value of the revision ID register through the wizard.

11

tabort_sig

Read/write

Signaled target abort. This bit is set when a local peripheral

device terminates a transaction. The function automatically

sets this bit if it issued a target abort after the local side

asserted

lt_abortn

. This bit is driven to the local side on

the

stat_reg

[1]

output.

12

tar_abrt_rec

Read/write

Target abort. When high,

tar_abrt_rec

indicates that the

function in master mode has detected a target abort from the

current target device. This bit is driven to the local side on the

stat_reg[2]

output.

13

mstr_abrt

Read/write

Master abort. When high,

mstr_abrt

indicates that the

function in master mode has terminated the current

transaction with a master abort. This bit is driven to the local

side on the

stat_reg[3]

output.

14

serr_set

Read/write

Signaled system error. When high,

serr_set

indicates

that the function drove the

serrn

output active, i.e., an

address phase parity error has occurred. The function

signals a system error only if an address phase parity error

was detected and

serr_ena

was set. This signal is driven

to the local side on the

stat_reg[4]

output.

15

det_par_err

Read/write

Detected parity error. When high,

det_par_err

indicates

that the function detected either an address or data parity

error. Even if parity error reporting is disabled (via

perr_ena

), the function sets the

det_par_err

bit. This

signal is driven to the local side on the

stat_reg[5]

output.

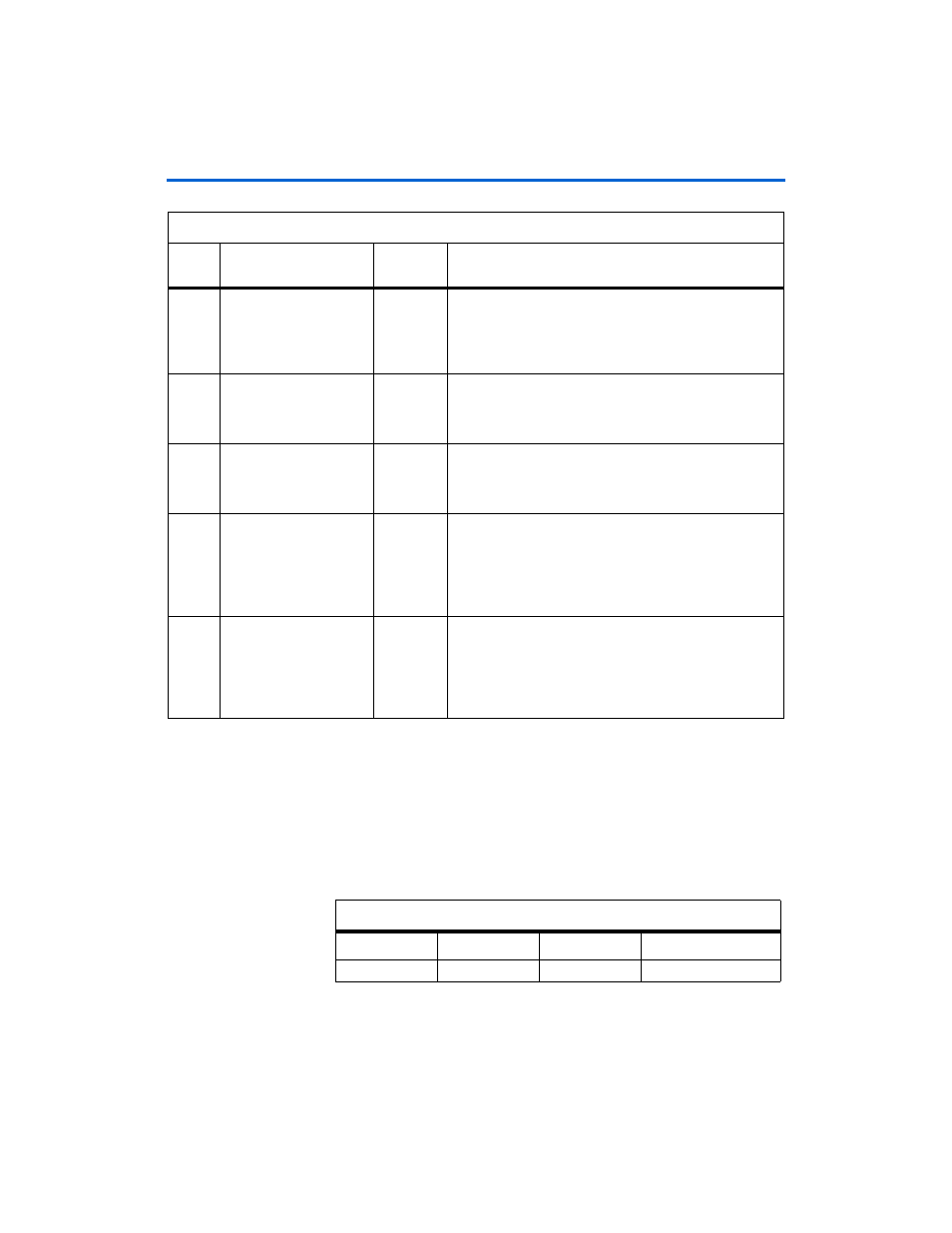

Table 3–17. Status Register Format (Part 2 of 2)

Data

Bit

Mnemonic

Read/Write

Definition

Table 3–18. Revision ID Register Format

Data Bit

Mnemonic

Read/Write

Definition

7..0

rev_id

Read

PCI revision ID