Altera PCI Compiler User Manual

Page 120

3–46

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Target Mode Operation

The pci_mt64 and pci_t64 MegaCore functions support the following

64-bit target memory transactions:

■

64-bit single-cycle memory read/write

■

64-bit burst memory read/write

Each PCI function supports the following 32-bit transactions:

■

32-bit single-cycle memory read/write

■

32-bit burst memory read/write

■

I/O read/write

■

Configuration read/write

1

The pci_mt64 and pci_t64 functions assume that the local

side is 64 bits during memory transactions and 32 bits during

I/O transactions. For memory read transactions, these functions

automatically read 64-bit data on the local side and transfer the

data to the PCI master, one DWORD at a time, if the PCI bus is 32

bits wide.

A read or write transaction begins after a master device acquires

mastership of the PCI bus and asserts framen to indicate the beginning

of a bus transaction. If the transaction is a 64-bit transaction, the master

device asserts the req64n signal at the same time as it asserts the framen

signal. The clock cycle where the framen signal is asserted is called the

address phase. During the address phase, the master device drives the

transaction address and command on ad[31..0] and cben[3..0],

respectively. When framen is asserted, the PCI MegaCore function

latches the address and command signals on the first clock edge and

starts the address decode phase. If the transaction address matches the

target, the target asserts the devseln signal to claim the transaction. In

the case of 64-bit transactions, the pci_mt64 and pci_t64 assert the

ack64n

signal at the same time as the devseln signal indicating that the

pci_mt64

and pci_t64 accepts the 64-bit transaction. All PCI

MegaCore functions implement slow decode (i.e., the devseln and

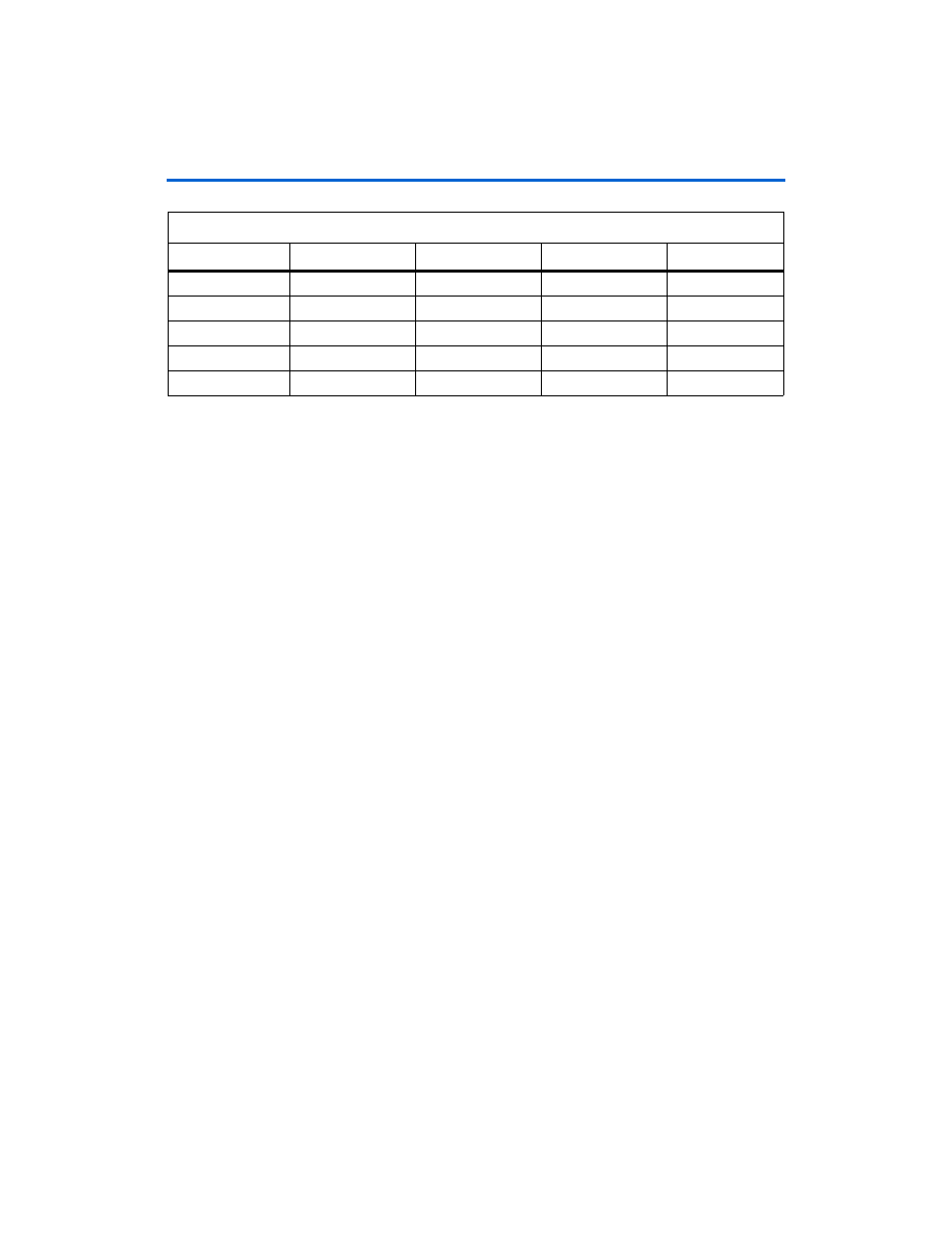

lm_rdyn

v

v

lm_adr_ackn

v

v

lm_ackn

v

v

lm_dxfrn

v

v

lm_tsr[9..0]

v

v

Table 3–34. PCI MegaCore Function Signals (Part 3 of 3)

Signal Name

pci_mt64

pci_t64

pci_mt32

pci_t32