Pci bus commands, Pci bus commands –27 – Altera PCI Compiler User Manual

Page 101

Altera Corporation

User Guide Version 11.1

3–27

October 2011

Functional Description

PCI Bus

Commands

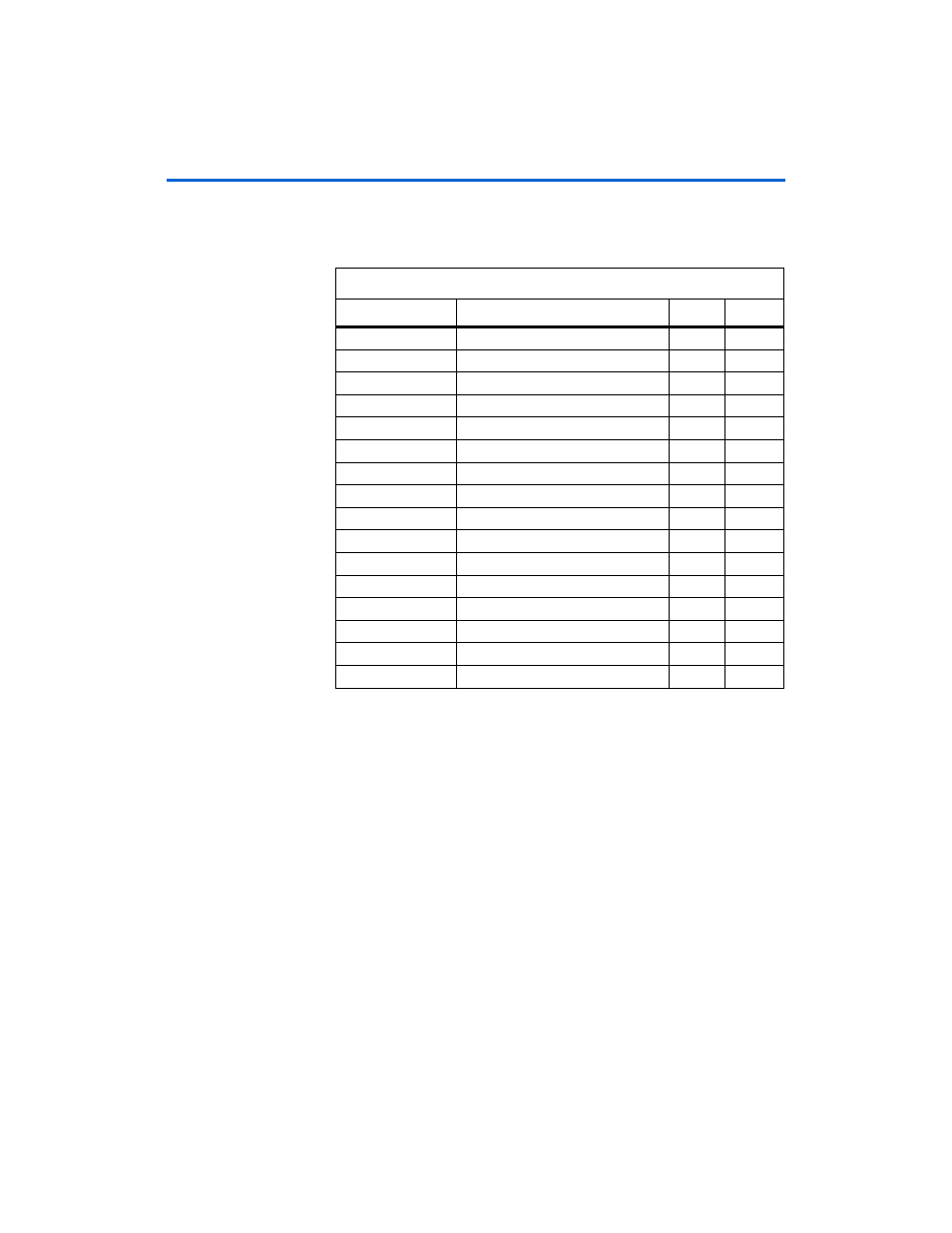

shows the PCI bus commands that can be initiated or

responded to by the PCI MegaCore functions.

During the address phase of a transaction, the cben[3..0] bus is used

to indicate the transaction type (

The PCI MegaCore functions respond to standard memory read/write,

cache-line memory read/write, I/O read/write, and configuration

read/write commands. The bus commands are discussed in greater detail

in

“Target Mode Operation” on page 3–44

.

Table 3–11. PCI Bus Command Support Summary

cben[3..0] Value

Bus Command Cycle

Master

Target

0000

Interrupt acknowledge

No

Yes

0001

Special cycle

No

Ignored

0010

I/O read

Yes

Yes

0011

I/O write

Yes

Yes

0100

Reserved

Ignored

Ignored

0101

Reserved

Ignored

Ignored

0110

Memory read

Yes

Yes

0111

Memory write

Yes

Yes

1000

Reserved

Ignored

Ignored

1001

Reserved

Ignored

Ignored

1010

Configuration read

Yes

Yes

1011

Configuration write

Yes

Yes

1100

Memory read multiple

Yes

Yes

1101

Dual address cycle (DAC)

Yes

Yes

1110

Yes

Yes

1111

Memory write and invalidate

Yes

Yes

:

(1)

Interrupt acknowledge support can be enabled on the Advanced PCI MegaCore

Function Features

page of the Parameterize - PCI Compiler wizard. When

support is enabled, the target accepts the interrupt acknowledge command and

aliases it as a memory read command.

(2)

The memory read multiple and memory read line commands are treated as

memory reads. The memory write and invalidate command is treated as a

memory write. The local side sees the exact command on the l_cmdo[3..0] bus

with the encoding shown in

.

(3)

This command is not supported by the pci_mt32 and pci_t32 MegaCore

functions.