Altera PCI Compiler User Manual

Page 140

3–66

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

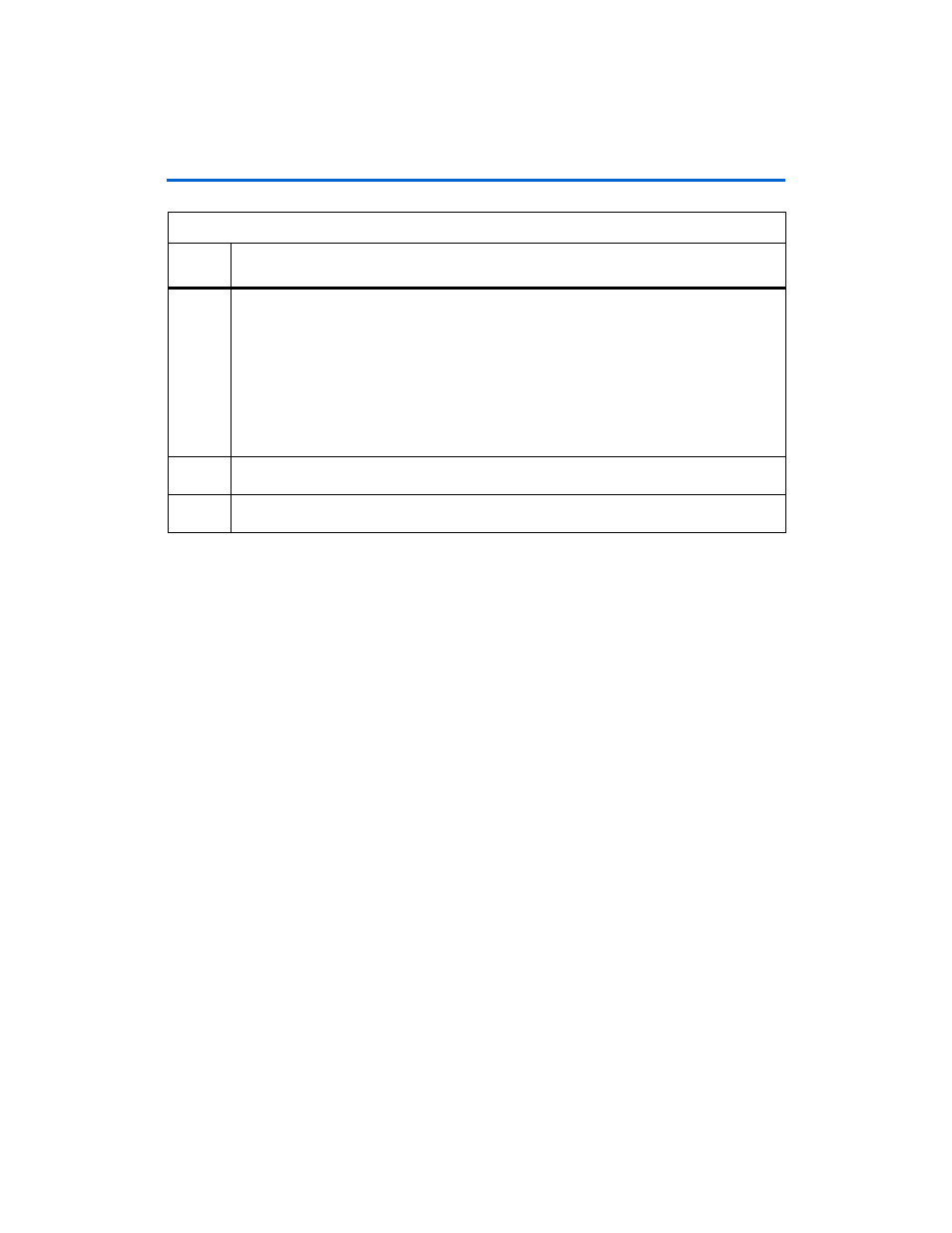

Target Mode Operation

7

The rising edge of clock cycle 7 registers the valid data from the

ad

bus and drives the data on the

l_dato

bus, registers valid byte enables from the

cben

bus, and drives the byte enables on the

l_beno

bus. At the same time, the PCI MegaCore function asserts the

lt_ackn

signal to indicate

that there is valid data on the

l_dato

bus and a valid byte enable on the

l_beno

bus. Because

lt_rdyn

is asserted during clock cycle 6 and

lt_ackn

is asserted in clock cycle 7, data will be

transferred in clock cycle 7.

lt_dxfrn

is asserted in clock cycle 7 to signify a local-side transfer.

lt_tsr

[10

] is asserted to indicate a successful data transfer on the PCI side during the previous

clock cycle. The PCI MegaCore function also deasserts

trdyn

,

devseln

, and

ack64n

to end the

transaction. To satisfy the requirements for sustained tri-state buffers, the PCI MegaCore function

drives

devseln

,

ack64n

,

trdyn

, and

stopn

high during this clock cycle.

8

The PCI MegaCore function resets all

lt_tsr[11..0]

signals because the PCI side has

completed the transaction. The PCI MegaCore function also tri-states its control signals.

9

The PCI MegaCore function deasserts

lt_framen

indicating to the local side that no additional

data is in the internal pipeline.

Table 3–36. Single-Cycle Memory Write Target Transactions (Part 2 of 2)

Clock

Cycle

Event