Altera PCI Compiler User Manual

Page 187

Altera Corporation

User Guide Version 11.1

3–113

October 2011

Functional Description

9

Because

irdyn

and

trdyn

are asserted, the second 64-bit data word is transferred to the PCI side

on the rising edge of clock cycle 10.

The function asserts

lm_ackn

to inform the local side that the PCI side is ready to accept data.

Because

lm_rdyn

was asserted in the previous cycle and

lm_ackn

is asserted in the current

cycle, the function asserts

lm_dxfrn

. The assertion of the

lm_dxfrn

,

l_ldat_ackn

, and

l_hdat_ackn

signals indicates to the local side that it has transferred one data word from the

l_adi

bus.

The function asserts

lm_tsr[8]

in the same clock cycle to inform the local side that a data phase

was completed successfully on the PCI bus during the previous clock cycle. The function also asserts

lm_tsr[9]

to inform the local side that the PCI target has claimed the 64-bit transaction with

ack64n

.

10

Because

irdyn

and

trdyn

are asserted, the third 64-bit data word is transferred to the PCI side on

the rising edge of clock 11.

The function asserts

lm_ackn

to inform the local side that the PCI side is ready to accept data.

Because

lm_rdyn

was asserted in the previous cycle and

lm_ackn

is asserted in the current

cycle, the function asserts

lm_dxfrn

. The assertion of the

lm_dxfrn

,

l_ldat_ackn

, and

l_hdat_ackn

signals indicates to the local side that it has transferred one data word from the

l_adi

bus. Also, the assertion of the

lm_lastn

signal indicates to the local side that valid data is

expected on the

l_adi

bus. Also, the assertion of the

lm_lastn

signal indicates that clock cycle

10 is the last data phase on the local side.

The function also asserts

lm_tsr[8]

in the same clock cycle to inform the local side that a

successful data transfer has occurred on the PCI bus during the previous clock cycle.

11

Because

lm_lastn

was asserted and a data phase was completed in the previous cycle, the

function deasserts

framen

and

req64n

and asserts

irdyn

to signal the last data phase. Because

trdyn

is asserted, the last data phase is completed on the PCI side on the rising edge of clock cycle

12.

On the local side, the function deasserts

lm_ackn

and

lm_dxfrn

since the last data phase on the

local side was completed on the previous cycle.

The function continues to assert

lm_tsr[8]

, informing the local side that a successful data transfer

has occurred on the PCI bus during the previous clock cycle.

12

The function deasserts

irdyn

and tri-states

framen

and

req64n

. The PCI target deasserts

devseln

,

ack64n

, and

trdyn

. These actions indicate that the transaction has ended and there

will be no additional data phases.

The function continues to assert

lm_tsr[8]

, informing the local side that a successful data transfer

has occurred on the PCI bus during the previous clock cycle.

13

The function deasserts

lm_tsr[3]

, informing the local side that the data transfer mode is

completed.

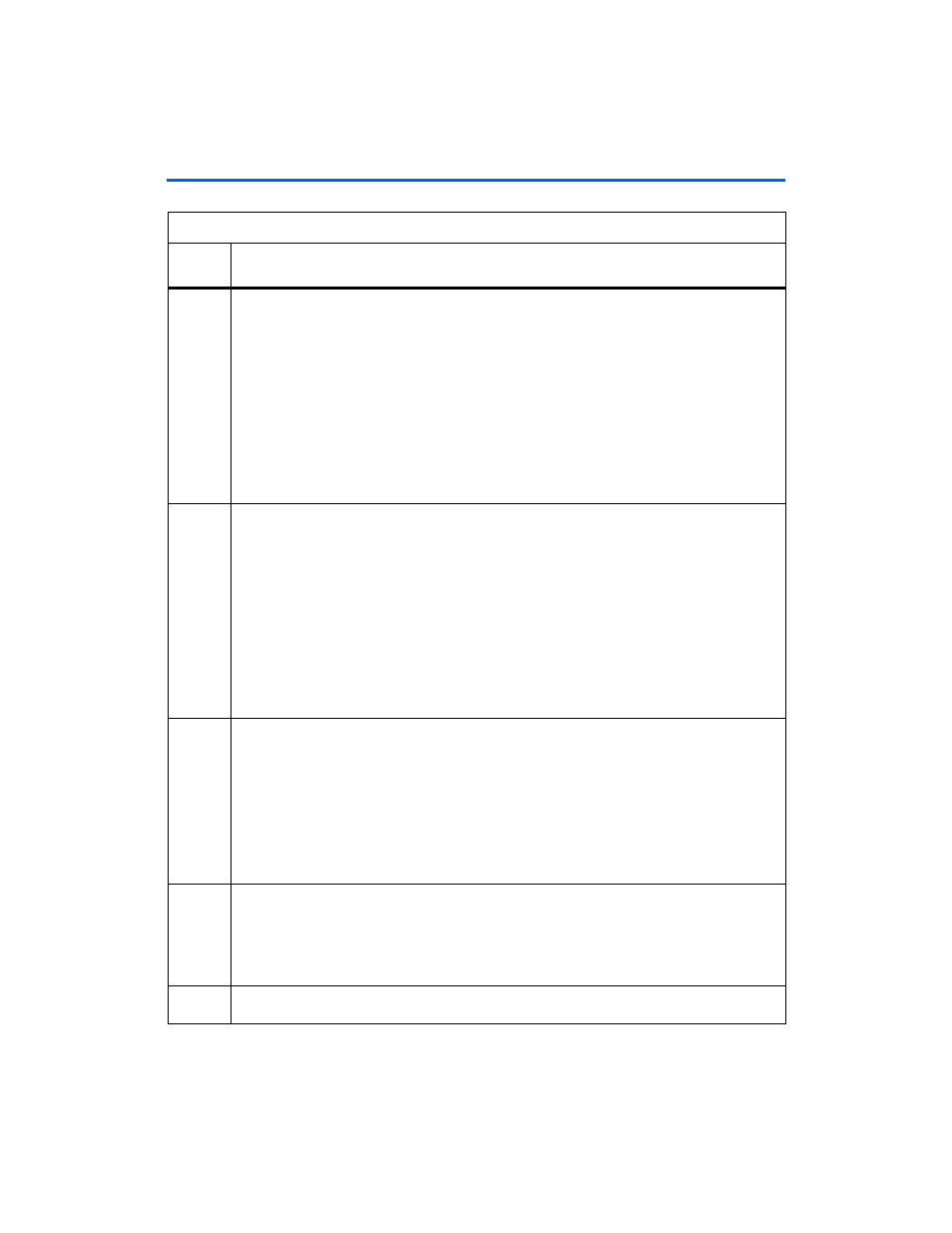

Table 3–39. Zero-Wait State Burst Memory Write Master Transaction (Part 3 of 3)

Clock

Cycle

Event