Local target, Dma engine – Altera PCI Compiler User Manual

Page 227

Altera Corporation

User Guide Version 11.1

4–17

October 2011

PCI Compiler

Testbench

Local Target

The local target consists of a simple state machine that performs 32- or

64-bit memory read/write transactions with the LPM memory and 32-bit

single-cycle I/O read/write transactions with an I/O register defined in

the local target. The local target uses prefetch logic for burst read

transactions and ignores byte enables for all memory and I/O

transactions.

shows the BAR2 register mapping.

Depending on the value of the target termination register, the local target

performs the terminations in

.

DMA Engine

The DMA engine has two 32-bit registers, which are mapped to BAR2 in

the PCI MegaCore function.

describes the mapping of DMA

registers on BAR2.

To initiate a master transaction from a PCI MegaCore function, use the

master transactor to perform memory writes to these locations with the

appropriate values.

The dma_sa register defines the system address used for the PCI

transaction. This address is driven during the address phase of the PCI

transaction. Normally, the address written here is the base address

register value of the PCI testbench target transactor.

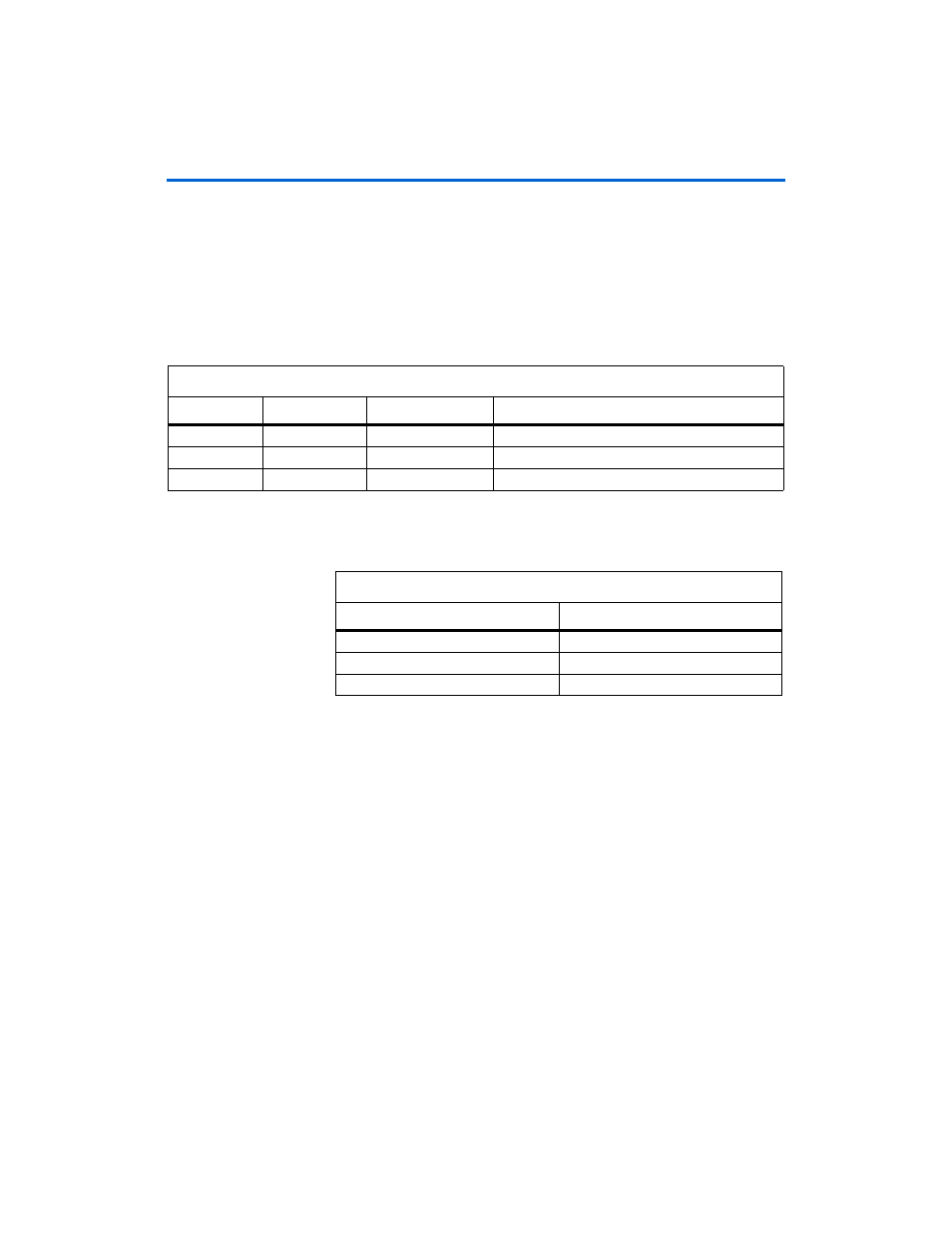

Table 4–9. BAR2 Register Mapping

Address Space Range Reserved

Mnemonic

Register Name

BAR2

00h-03h

targ_termination_reg Target termination register.

BAR2

04h-07h

dma_sa[31:0]

DMA system address register

BAR2

08h-0Bh

dma_bc_la[31:0]

DMA byte count and local address register

Table 4–10. Target Terminations

targ_termination_reg Setting

Target Termination

xxxxxxx0

Normal Termination

xxxxxxx1

Target Retry

xxxxxxx2

Disconnect