Altera PCI Compiler User Manual

Page 312

7–44

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

PCI Master Operation

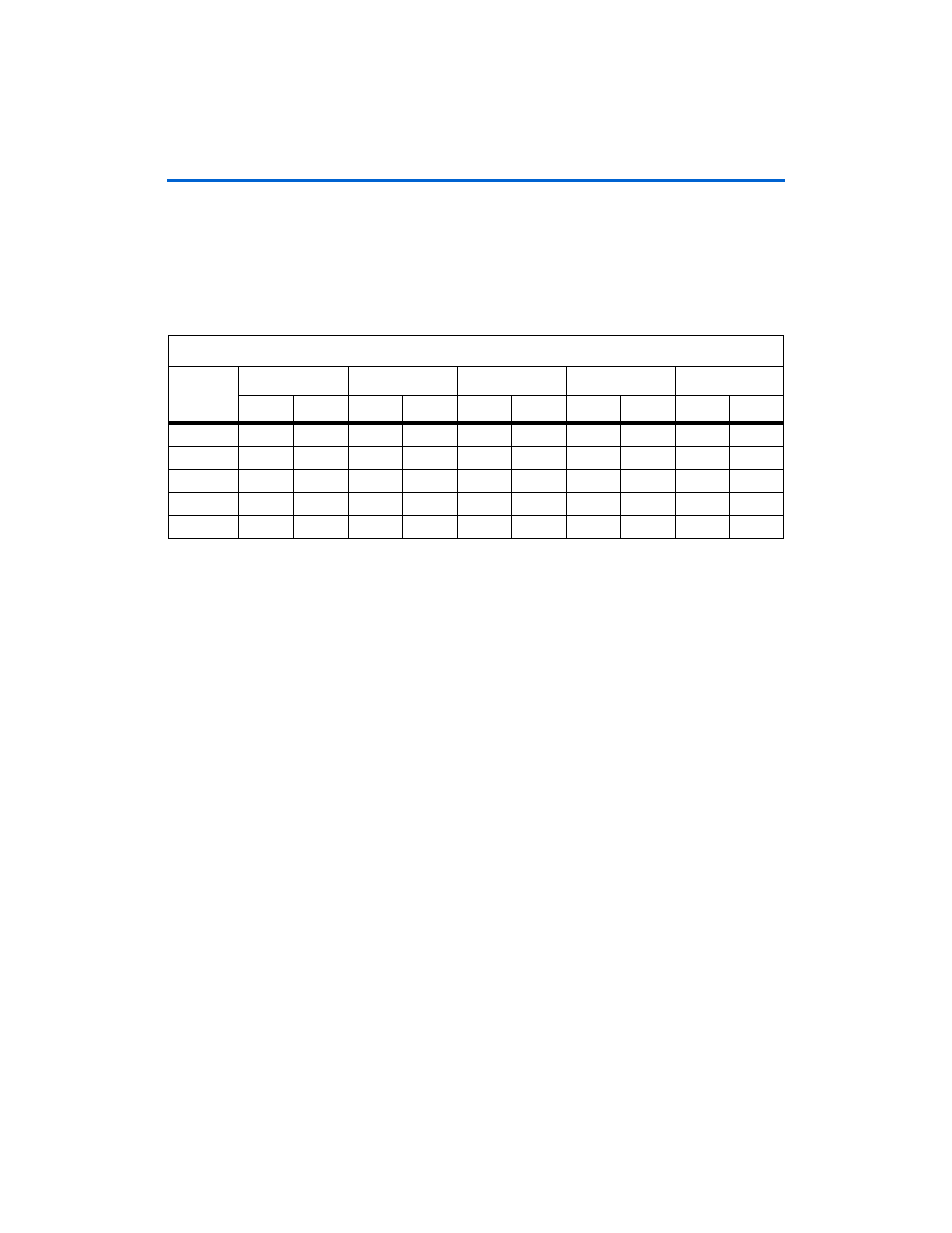

specifies the ordering rules and behavior for the

PCI-to-Avalon direction. The entries in this table describe whether a type

in a row may pass a type in a column. The table uses the following

terminology: "No" means a type may not pass another type, "Yes/No"

means a type may pass the other type, but does not have to, and "Yes"

means that a type must pass another type to avoid deadlocks.

Table 7–15. Summary of Ordering in the PCI-to-Avalon Direction

PMW

DRR

DWR

DRC

DWC

Impl

Spec

Impl

Spec

Impl

Spec

Impl

Spec

Impl

PMW

No

Yes

Yes

N/A

Yes

Yes

Yes

Yes

DRR

No

No

Yes/ No

Yes/ No

N/A

Yes/ No

Yes

Yes/ No

Yes

DWR

No

No

Yes/ No

Yes/ No

Yes/ No

Yes

Yes/ No

No

DRC

No

Yes

Yes

N/A

Yes/ No

No

Yes/ No

No

DWC

Yes/ No

Yes

Yes

No

Yes/ No

No

Yes/ No

No

Notes to

(1)

Spec

refers to the PCI Local Bus Specification, Revision 3.0, published by PCI-SIG.

(2)

Impl

refers to the implementation of this passing rule in the PCI-Avalon bridge.

(3)

PMWs and DRRs cannot pass other PMWs in the PCI-to-Avalon Command/Write Data buffer. Ordering logic will

prevent PMWs that hit prefetchable BARs and PMWs that hit non-prefetchable BARs from passing each other.

(4)

The ordering logic prevents DRCs from passing PMWs

(5)

Avalon-MM does not provide any mechanism to stop accepting reads separately from writes, so there is no way

to make PMWs, DRCs (or other DRRs) pass DRRs. However, since Avalon-MM provides completely separate

paths for master and slave transactions, the PCI requirements for this passing do not apply.

(6)

PMWs and DRRs in the PCI-to-Avalon Buffers are allowed to pass DRCs in the Read Response buffers.

(7)

Avalon-MM requires the DRCs (Read Responses) be returned in the order the requests were made. Note, however,

that DRCs may actually be returned in a different order than they completed on the PCI bus.