Burst memory write master transactions – Altera PCI Compiler User Manual

Page 184

3–110

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Master Mode Operation

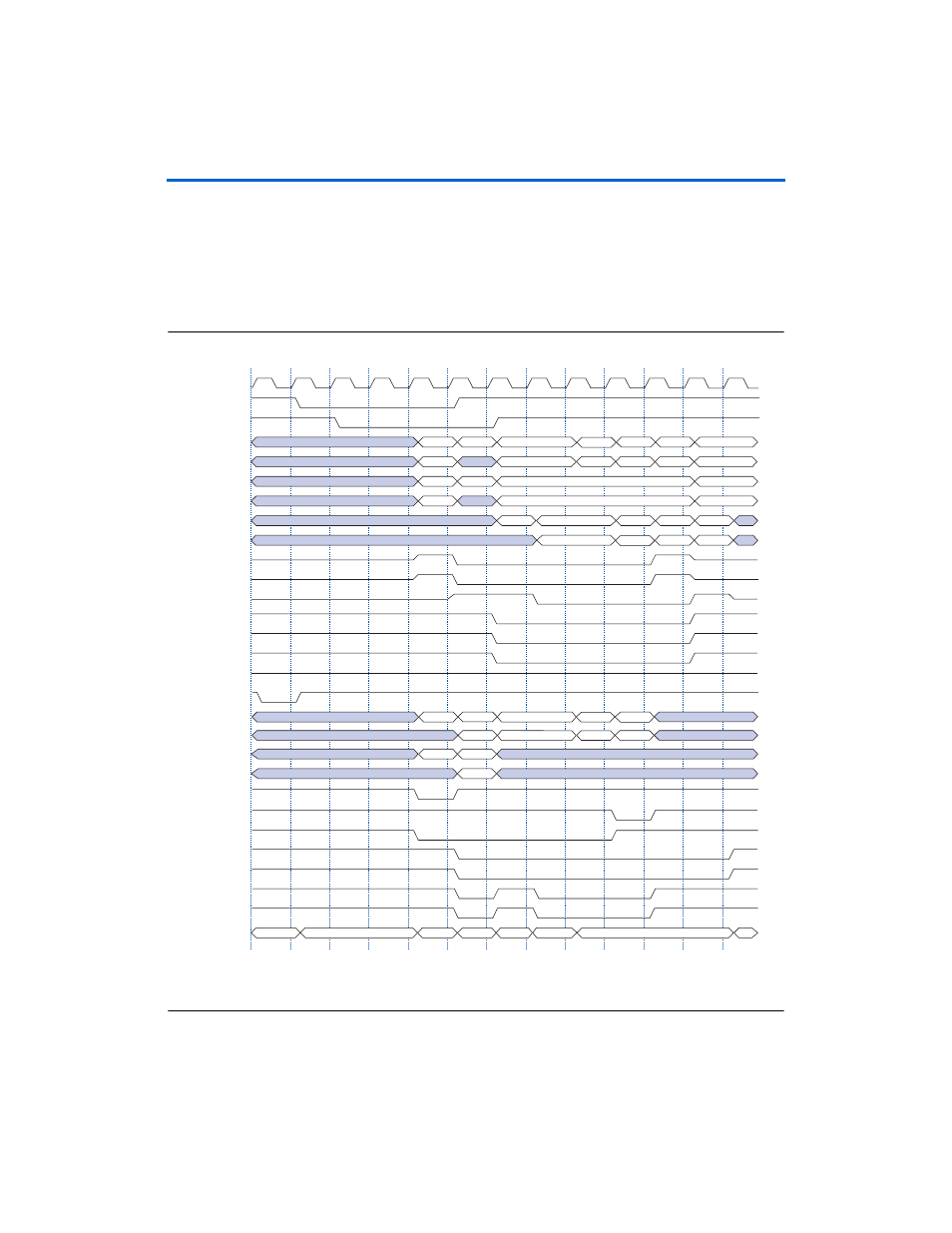

Burst Memory Write Master Transactions

shows the waveform for a 64-bit zero-wait state burst

memory write master transaction. This figure applies to both pci_mt64

and pci_mt32 MegaCore functions, excluding the 64-bit extension

signals as noted for pci_mt32. In this transaction, four 64-bit QWORDs are

transferred from the local side to the PCI side.

Figure 3–38. Zero-Wait State Burst Memory Write Master Transaction

Notes to

:

(1)

This signal is not applicable to the pci_mt32 MegaCore function.

(2)

For pci_mt32, lm_req32n should be substituted for lm_req64n for 32-bit master transactions.

2

3

4

5

6

7

9

10

12

clk

reqn

8

11

1

gntn

ad[31..0]

(1) ad[63..32]

cben[3..0]

(1) cben[7..4]

par

(1) par64

framen

(1) req64n

irdyn

devseln

(1) ack64n

trdyn

stopn

Adr

7

Adr-PAR

BE_L

D0_L

0

0

0

0

D2_L

D3_L

13

l_adi[31..0]

Adr

7

(1) l_adi[63..32]

D0_H

D0_L

D3_H

D3_L

D1_L

D1_H

l_cbeni[3..0]

BE_L

(1) l_cbeni[7..4]

BE_H

(1), (2) lm_req64n

lm_lastn

lm_adr_ackn

lm_rdyn

lm_tsr[9..0]

000

001

004

002

308

008

208

000

(1) l_ldat_ackn

(1) l_hdat_ackn

lm_ackn

lm_dxfrn

D0_H

Z

D2_H

D3_H

BE_H

D0-L-PAR

D2-L-PAR

D3-L-PAR

D0-H-PAR

D2-H-PAR

D3-H-PAR

Z

Z

Z

D1_L

D1_H

D1-L-PAR

D1-H-PAR

D2_L

D2_H