Reset control word, Reset control word –57 – Altera CPRI IP Core User Manual

Page 89

Chapter 4: Functional Description

4–57

CPRI Protocol Interface Layer (Physical Layer)

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

The frame synchronization machine detects LOS and LOF directly. You can program

your application to detect and respond to RAI and SDI errors as appropriate. Refer to

“Accessing the Hyperframe Control Words” on page 4–42

for information about

retrieving these alarms from the hyperframe control word.

The CPRI IP core handles incoming reset requests on the CPRI link by signalling the

application to assert the reset signal to reset the IP core. The application reads the

requests using the CPU interface. The following section describes the additional

support the CPRI IP core provides to process this special command.

Reset Control Word

A CPRI IP core in master clocking mode can send a reset request through the CPRI

link and a CPRI IP core in slave clocking mode can receive a reset request through the

CPRI link. As required by the CPRI specification, the reset control information is sent

in bit 0 of the CPRI hyperframe control word Z.130.0. This reset bit communicates

both reset request and reset acknowledge.

Table 4–16

lists the signals and register fields that determine the CPRI IP core’s

response to a reset request received on the CPRI link and that determine whether it

sends a reset request on the CPRI link.

A CPRI IP core in master mode transmits a reset request to the RE slave nodes to

which it is connected under either of the trigger conditions shown in

Table 4–16

. The

behavior of a CPRI IP core in slave mode that receives a reset request on the CPRI link

depends on the same enable fields in its own

CPRI_HW_RESET

register. For reset

acknowledgements, as for the original reset request conditions, if the

reset_hw_en

bit

is asserted, the

reset_gen_en

bit is ignored.

The CPRI specification requires that the Z.130.0 reset bit must be detected by the CPRI

partner in ten consecutive hyperframes before the CPRI partner confirms the reset

request. The reset generation request is in effect while the condition that triggered the

reset request remains in effect, until the reset acknowledge control bit is detected on

the incoming CPRI link.

To abort a reset request, set or reset a register field to negate the condition. Specifically,

to abort a reset request made by asserting the

reset_gen_force

bit in the

CPRI_HW_RESET

register, set the

reset_gen_en

bit of the

CPRI_HW_RESET

register to 0. To

abort a reset request made by asserting the

hw_reset_assert

input signal, set the

reset_hw_en

bit of the

CPRI_HW_RESET

register to 0.

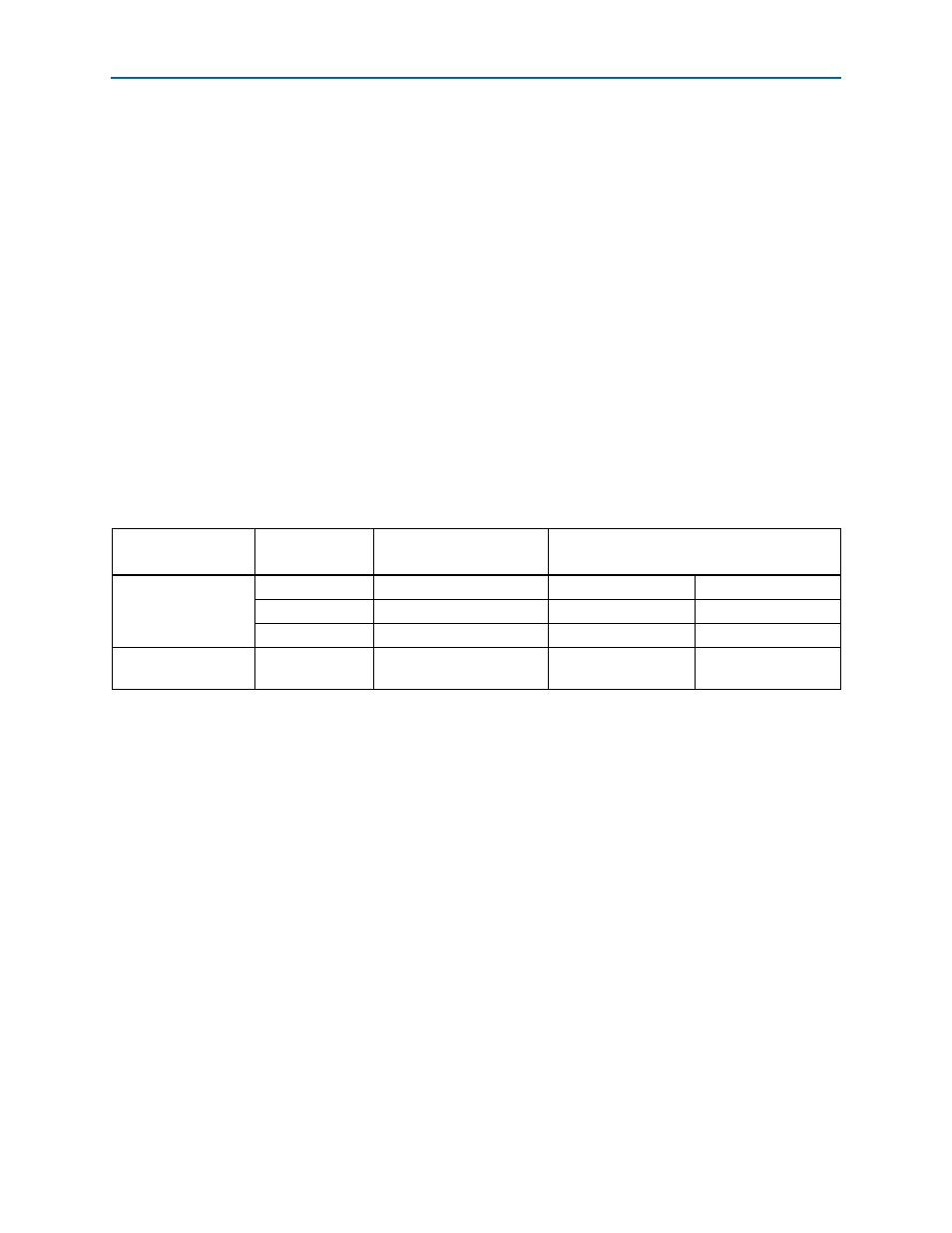

Table 4–16. Conditions That Trigger a Reset Request or Enable a Reset Acknowledge on the CPRI Link

Register or Signal

Name

Register Bits

Field Name

Trigger Conditions for Sending Reset

Request (Master) or ACK (Slave)

CPRI_HW_RESET

)

[0]

reset_gen_en

1

—

[1]

reset_gen_force

1

—

[3]

reset_hw_en

0

1

hw_reset_assert

)

—

—

—

1