Altera CPRI IP Core User Manual

Page 112

6–14

Chapter 6: Signals

Physical Layer Signals

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

In Cyclone IV GX devices, channel reconfiguration is enabled to support autorate

negotiation.

Table 6–13

lists the signals implemented in CPRI IP cores targeted to

Cyclone IV GX devices to support scan-chain based reconfiguration.

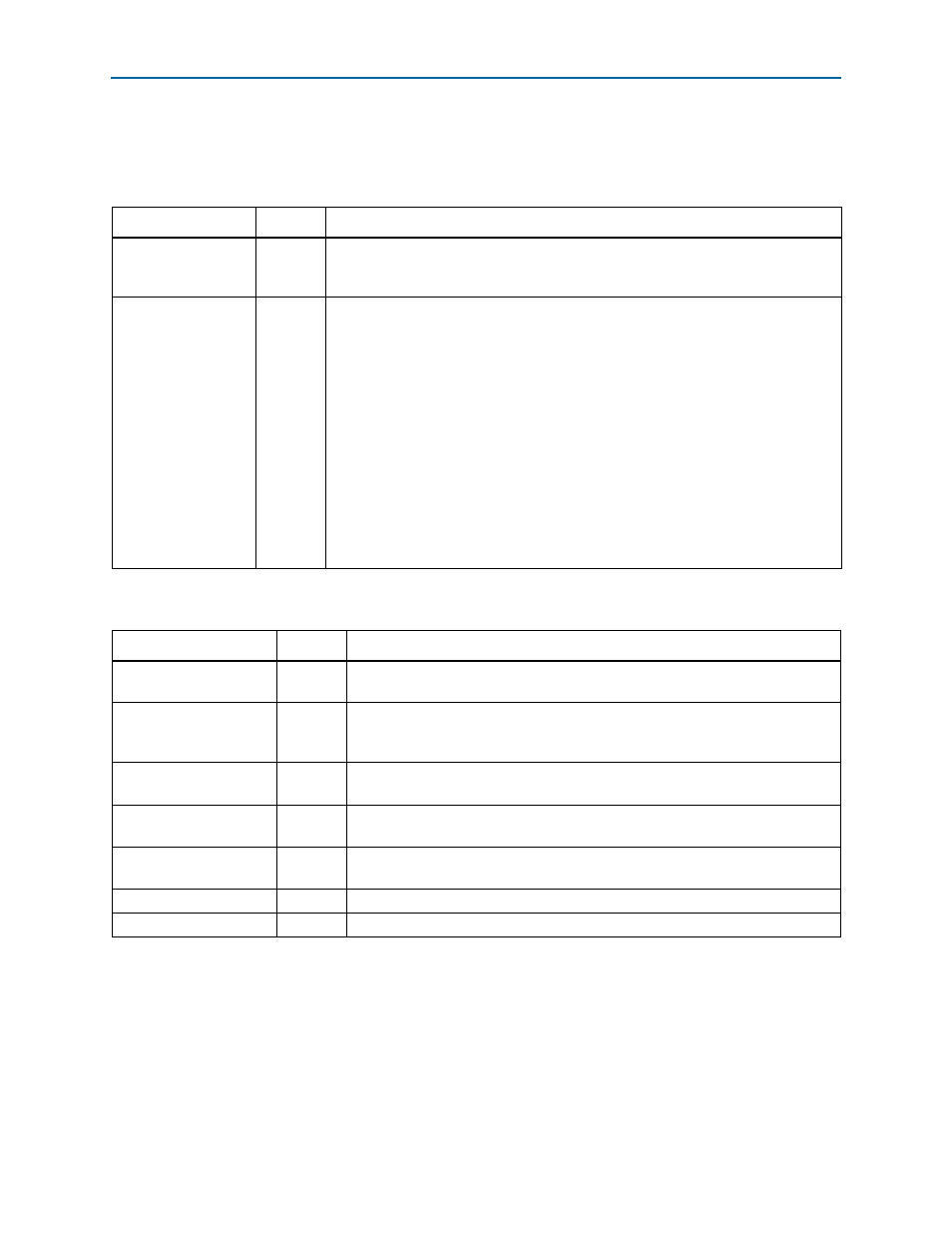

Table 6–12. Autorate Negotiation Signals

Signal

Direction

Description

datarate_en

Output

Indicates whether autorate negotiation is enabled. This signal reflects the value in the

i_datarate_en

field of the

AUTO_RATE_CONFIG

datarate_set[4:0]

Output

CPRI line rate to be used in next attempt to achieve frame synchronization. This signal

reflects the value currently in the

i_datarate_set

field of the

AUTO_RATE_CONFIG

The CPRI line rate is encoded in this field with the following values:

00001: 614.4 Mbps

00010: 1228.8 Mbps

00100: 2457.6 Mbps

00101: 3072.0 Mbps

01000: 4915.0 Mbps (not supported for Cyclone IV GX and Cyclone V GX devices)

01010: 6144.0 Mbps (not supported for Cyclone IV GX and Cyclone V GX devices)

10000: 9830.4 Mbps (supported only for Stratix V GX, Stratix V GT, Arria V GT, and

Arria V GZ devices)

Table 6–13. Scan-Chain Based Reconfiguration Interface Signals For CPRI Autorate Negotiation in Cyclone IV GX

Devices

Signal

Direction

Description

pll_areset

Input

Resets the PLL. Signal must be asserted after PLL reconfiguration. Connect to the

areset

signal for the PLL.

pll_configupdate

Input

When this signal is asserted, the PLL counters are updated with the contents of the

scan chain. Signal is asserted for a single

pll_scanclk

cycle. Connect to the PLL

reconfiguration scan chain

configupdate

signal.

pll_scanclk

Input

Clocks the shift registers in the PLL reconfiguration scan chain.The maximum

frequency of this clock is 100 MHz.

pll_scanclkena

Input

Indicates scan data can be shifted in on the following

pll_scanclk

cycle. Connect

to the PLL reconfiguration scan chain

scanclkena

signal.

pll_scandata

Input

Serial data scanned into the scan chain. Connect to the PLL reconfiguration scan

chain

scandata

signal.

pll_reconfig_done

Output

Indicates PLL reconfiguration is complete.

pll_scandataout

Output

Output stream shifted out of the scan chain.