Mii receiver, Mii receiver –39, Figure 4–22 – Altera CPRI IP Core User Manual

Page 71

Chapter 4: Functional Description

4–39

Media Independent Interface to an External Ethernet Block

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

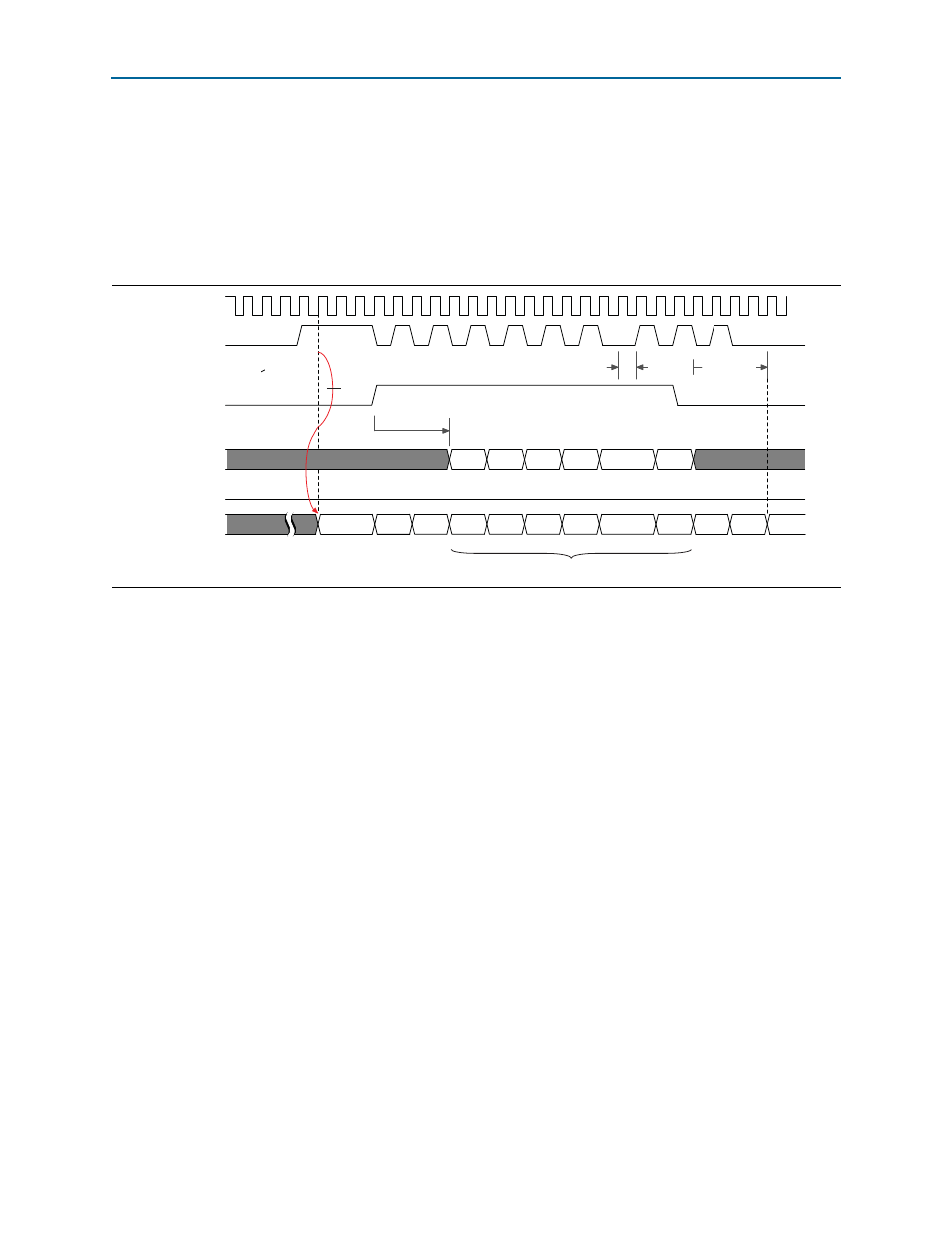

illustrates the MII transmitter protocol with no input errors. The

cpri_mii_txen

signal remains asserted for the duration of the packet transfer.

Although

cpri_mii_txrd

can be reasserted every other cycle during transmission of

an Ethernet packet on

cpri_mii_txd

, this need not always occur. The CPRI MII

transmitter can deassert

cpri_mii_txrd

for more than one cycle to backpressure the

external Ethernet block. In that case, the external Ethernet block must maintain the

data value on

cpri_mii_txd

until the cycle following reassertion of

cpri_mii_txrd

.

If

cpri_mii_txen

is deasserted while

cpri_mii_txrd

is deasserted, and is not

reasserted in the cycle following the reassertion of

cpri_mii_txrd

, then the CPRI MII

transmitter inserts a T symbol in the packet; therefore, the external Ethernet block

must reassert

cpri_mii_txen

in the cycle following reassertion of

cpri_mii_txrd

,

during transmission of an Ethernet packet on

cpri_mii_txd

.

For more information about the MII transmitter module, refer to

Transmitter Signals” on page 6–10

.

MII Receiver

The MII receiver module receives data from the CPRI link by reading it from the CPRI

receiver module. It performs 4B/5B decoding on the 5-bit data values before

transmitting them as 4-bit data values on the MII.

After the CPRI IP core achieves frame synchronization, the MII receiver module can

send data to the external Ethernet block. The MII receiver module transmits the K

nibble to indicate start-of-frame on the MII. The J nibble of the start-of-frame is

consumed by the CPRI IP core, and is not transmitted on the MII.

Figure 4–22. CPRI MII Transmitter Example

cpri_mii_txclk

cpri_mii_txrd

cpri_mii_txen

cpri_mii_txd[3:0]

cpri_mii_txer

decoded result

(conceptual)

txrd asserted

>1 cycle

without

txen response

> IDLEs

No txen response

to 2 cycles

in which

txrd asserted

txrd is deasserted

an additional cycle

to backpressure the Ethernet block

Idle

J

K

D0

D0

D1

D1

D2

D2

D3

D3

D4

D4

D5

T

R

Idle

D5

Ethernet packet

txen asserted

2 cycles in which

txrd is asserted

txen is asserted

>1 cycle

after

txrd assertion