Altera CPRI IP Core User Manual

Page 146

7–30

Chapter 7: Software Interface

HDLC Registers

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

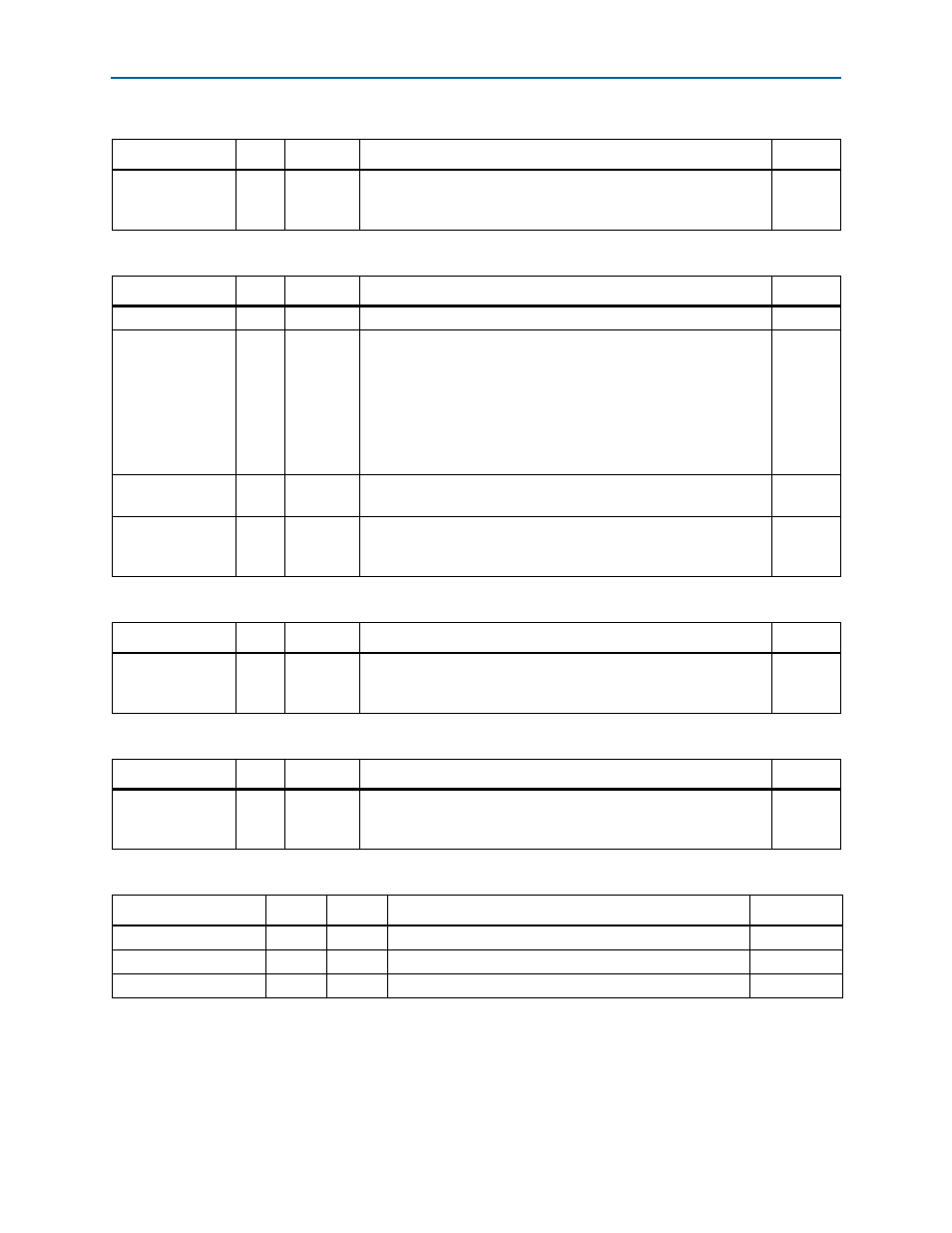

Table 7–74. HDLC_RX_DATA_WAIT—HDLC Rx Data with Wait-State Insertion—Offset: 0x318

Field

Bits

Access

Function

Default

rx_data

[31:0] RO

HDLC Rx frame data. If the HDLC receiver module takes HDLC data

from this register, it inserts wait states on the HDLC channel until

data is ready, unless the CPU times out the operation.

1'h0

Table 7–75. HDLC_TX_CONTROL—HDLC Tx Control—Offset: 0x31C

Field

Bits

Access

Function

Default

RSRV

[31:4] UR0

Reserved.

28'h0

tx_length

[3:2]

RW

Length of the final word in the packet. Values are:

00: 1 valid byte

01: 2 valid bytes

10: 3 valid bytes

11: 4 valid bytes

This field is valid when the

tx_eop

bit is asserted.

1’h0

tx_discard

[1]

WO

Indicates that the HDLC transmitter module should discard the

current HDLC Tx frame.

1'h0

tx_eop

[0]

RW

Indicates that the next data word to be written to the

HDLC_TX_DATA

or

HDLC_TX_DATA_WAIT

register contains the end-of-packet byte for

this Tx packet.

1’h0

Table 7–76. HDLC_TX_DATA—HDLC Tx Data—Offset: 0x320

Field

Bits

Access

Function

Default

tx_data

[31:0] RW

HDLC Tx frame data. If the HDLC transmitter module writes HDLC

data to this register, if data is not ready when the module expects it,

the HDLC transmitter module aborts the packet.

1'h0

Table 7–77. HDLC_TX_DATA_WAIT—HDLC Tx Data with Wait-State Insertion—Offset: 0x324

Field

Bits

Access

Function

Default

tx_data

[31:0] RW

HDLC Tx frame data. If the HDLC transmitter module writes HDLC

data to this register, it waits until data is ready, unless the CPU times

out the operation.

1'h0

Table 7–78. HDLC_RX_EX_STATUS—HDLC Rx Additional Status—Offset: 0x328

Field

Bits

Access

Function

Default

RSRV

[31:7]

UR0

Reserved.

25'h0

CRC_error

[6]

RC

Indicates that an HDLC frame with a CRC error was received.

1'h0

RSRV

[5:0]

UR0

Reserved.

6'h0